Volume: 08 Issue: 06 | June 2021 www.irjet.net

p-ISSN: 2395-0030

# DESIGN OF ENHANCED HALF RIPPLE CARRY ADDER FOR VLSI ACCOMPLISHMENT OF TWO-DIMENSIONAL DISCRETE WAVELET TRANSMUTE

## Nitu Kumari<sup>1</sup>, Shailesh Kumar Singh<sup>2</sup>

<sup>1</sup>Student M.Sc(Physics),Monad University, Hapur <sup>2</sup>Associate Professor, Department of Physics, HimalayanGarhwal University Uttarakhand

**Abstract** - *The purpose of the modern studies paintings is* to layout an green -dimensional Discrete Wavelet Transformation (DWT)primarily based totally picture compression approach. In order to obtain quality performance, Enhanced Half-Ripple Carry Adder (EHRCA) has been designed. Verilog Hardware Description Language (Verilog HDL) is used to version the EHRCA and DWT approach.DWT approach has been designed with the assist of varieties of filtering approach called Low Pass Filter (LPF) and High Pass Filter (HPF). Three degrees of decomposition is made via way of means of DWT method and every method have degrees compressions called "Row Wise Compression" and "Column Wise Compression". In proposed DWT models, adders are recognized as excessive capability than different components. In order to enhance the performance of DWT method, an green adder called "Enhanced Half-Ripple Carry Adder (EHRCA)" has been designed on this studies paintings. Proposed EHRCA circuit offers 10.71% upgrades in hardware slice utilization, 11.78% upgrades in general strength intake than traditional Binary to Excess 1 Conversion (BEC) primarily based totally Square Root Carry Select Adder (SQRT CSLA). Further proposed adder has been integrated into Row Wise Compression and Column Wise Compression for enhancing the architectural performances of DWT. In future, proposed EHRCA primarily based totally DWT can be beneficial in Discrete Cosine Transformation (DCT) and hybrid kind and lifting primarily based totally DWT techniques.

*Key Words*: Binary to Excess 1 Conversion based Carry Select Adder, Carry Select Adder, Hybrid and Lifting based Discrete Wavelet Transformation Technique, Row and Column Wise Compression, Very Large Scale Integration

#### 1. INTRODUCTION

Two Dimensional (2-D) Discrete Wavelet Transformation strategies (DWT) are extensively used for photograph and video compression manner 5. The 2-D DWT method has multi-decision decomposition capability, as it performs role in lots of engineering fields 10. However, accumulation of big values of statistics of diverse decomposition stages of the remodel makes their complexity computationally very intensive. Large endeavours were designed many architectures that are aimed toward presenting excessive pace 2-D DWT computation with the requirement of

reasonable hardware utilization. These architectures may be classified as separable and non-separable architectures. In a separable structure, 2-D filtering operation may be done via 1-D filtering operations, one for processing the statistics in row-smart and some other one for processing the statistics in column-smart. The decomposition stages of input pictures may be hired through both a Recursive Pyramid Algorithm (RPA) or lights operation. In separable filtering structure a 1-D filtering shape is used to computational complexity among 1-D filtering processes. This will increase the latency in addition to reminiscence size of the architectures. The non-separable architectures are used to lessen the predicament of separable architectures, considering the fact that in non-separable architectures, 2-D DWT are computed without delay through the usage of 2-D filters. However, the pace of the DWT manner may be very low for non-separable architectures. In order to triumph over this problem, pipelining method is utilized in DWT structure10.

In general, Haar Discrete Wavelet Transform (HDWT) is used to compress the signal/photograph6. To boom the compression capacity of photograph, precision-conscious self quantizing architectures may be utilized in 3.To generate the DWT coefficients, Distributed Arithmetic (DA) primarily based totally Multiplication is utilized in 2. DA primarily based totally multiplier performs the multiplication operation with the assist of Look up Tables (LUTs). Therefore, the overall performance of DA primarily based totally multiplier is higher than every other multiplier. In 9, one dimensional DWT strategies may be applied in Very Large Scale Integration (VLSI) System layout environment. Further, VLSI primarily based totally excessive pace 2-D DWT can be applied in 1.

In this paper, 2-D DWT method is designed through the usage of Enhanced Half Ripple Carry Adder (EHRCA). An EHRCA is the kind of Ripple Carry Adder (RCA), hardware complexity and energy intake is reduced successfully than conventional RCA circuit. Also, the performance of DWT may be elevated in phrases of silicon are a and energy intake, while EHRCA incorporated into DWT manner.

# 2. DISCRETE WAVELET TRANSFORAMTION (DWT)

Volume: 08 Issue: 06 | June 2021

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

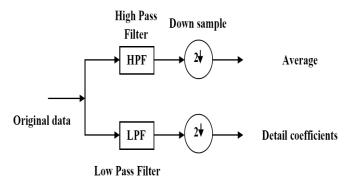

Discrete ripple Transformation (DWT) is that the technique for decomposing/compressing the images. additionally DWT represents as a picture that is the total of wavelet functions (wavelets) with completely different location and scale. It represents the info into a collection of low pass and high pass constants. The input file is suffered set of low pass and high pass filters. The output from high pass filters and low pass filters are down sampled by 2. The output from low pass filter is a median coefficient and therefore the output from high pass filter may be a detail coefficient. The schematic diagram of 1-D DWT technique is shown in Figure. 1.

Figure 1. Block diagram of 1-D DWT.

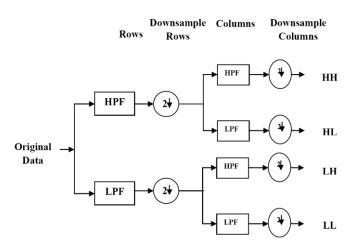

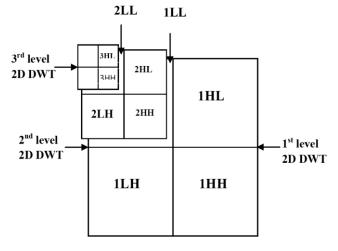

In a combine of-D DWT, the computer file is saw set of {every} low pass and high pass filter in a pair of directions, each rows and columns. As in 1-D DWT, the outputs from low pass and high pass filters are down sampled by 2 in every direction. Figure 2 shows the diagram of 2-D DWT. As in Figure 2, the output is in set of four constants LL, HL, opening cell-stimulating secretion and HH. In constant illustration, the first alphabet represents the rework in row where as a result of the second alphabet represents rework in column. The representation L means low pass signal and H means that high pass signal. throughout this paper, three levels of decomposition are done to compress the image with the help of EHRCA. The structure of DWT levels is shown in Figure 3. Similarly, in reconstruction, computer file is also achieved in multiple resolutions by rotten the LL constant any for numerous levels. The compressed data is up-sampled by a component of 2 therefore on reconstruct the initial input data whereas humanistic discipline interpolation process.

Figure 2. Block diagram of 2-D DWT.

Figure 3. Structure of DWT levels.

#### 3. Image Compression using DWT

An input image is older a series of filters to calculate the DWT coefficients. The procedure starts with passing this image through a half band digital low pass filter with impulse response h[n]. Filtering a picture signal corresponds to the numerical operation of convolution of an image signal with the impulse response of the filter. The convolution operation in distinct time is outlined as follows:

$$y(n) = \sum_{k=-\infty}^{\infty} x[k] \bullet h[n-k]$$

(1)

A half band low pass filter removes all frequencies that are above 1/2 the very best frequency within the signal, which may be taken as losing half of the information. Resolution, Volume: 08 Issue: 06 | June 2021 www.irjet.net p-ISSN: 2395-0072

on the opposite hand, is related to the number of knowledge within the signal, and so it's littered with filtering operations. However, sub sampling operation doesn't have an effect on the resolution when filtering,

$$y(n) = \sum_{k=-\infty}^{\infty} h[k] \bullet x[2n-k]$$

(2)

since; removing 1/2 the spectral elements from the sign makes half the quantity of samples redundant anyway. In summary, half band low pass filtering halves the resolution, however leaves the size unchanged. This signal is then sub sampled by Equation (2), therefore half of the number of samples are redundant. The procedure for sub sampling will mathematically be expressed as follows

The input image signals are rotten into average information and detail data. the typical and detail information are represented as follows

In Equations (3) and (4), g[k] and h[k] are represented as detail and average signals. In reconstruction, reverse method is applied to recover the initial image.

$$x[n] = \sum_{k=-\infty}^{\infty} \left( y_{high}[k] \bullet g[2k-n] \right) + \left( y_{low}[k] \bullet h[2k-n] \right)$$

(5)

In general, DWT is enforced in 2 styles of methods. they're 1. matrix operation technique and 2. equation Method. In linear equation methods, each set of 4 pixels are thoughtabout to figure the DWT coefficients. These four pixels are processed Equation by victimisation (6),

$$DWT_{coeff} = (Pixel_1 + Pixel_2 + Pixel_3 + Pixel_4)/2$$

(6)

From Equation (6), it's clear that, addition process is needed for compression in DWT for each level. To implement second DWT, EHRCA adder is employed in our work.

#### 4. Conventional Carry Select Adder

Carry choose Adder (CSLA) is one amongst the most effective adders for binary addition. In CSLA architecture, twin RCA is employed for carry input zero and carry input one respectively. additional Multiplexors are employed in ending of addition process. one RCA structure has four ranges of Full Adders (FAs). Therefore, dual RCA structure has eight numbers of FAs. additional number of gates is needed to style the CSLA for binary addition. typically this adder is termed as root Carry choose Adder (SQRT CSLA), because, it needs  $\sqrt{n}$  set of dual RCA set to work out N-bit binary addition process. All set of twin RCA will execute in a very parallel manner, ending of SORT CSLA uses the multiplexors to supply the ultimate total results. Hence, final stage solely has Carry Propagation Delay(CPD), however in RCA circuit, entire structure has CPD

e-ISSN: 2395-0056

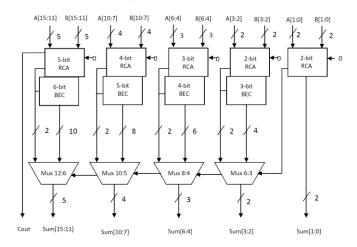

Figure 4. Structure of 16-bit BEC based SQRT CSLA.

Further, RCA circuit for carry input one has been replaced to Binary to Excess 1 (BEC) convertor to boost the performance. BEC circuit utilizes the less range of gates to perform the RCA operation for carry input 1. For instance, 16-bit BEC based mostly SQRT CSLA is illustrated in Figure 4. It consists of 4 set of RCA-BEC set to feature 2 16-bit binary integers. It reduces the semiconductor space utilization and power consumption than ancient SQRT CSLA circuit. However, silicon area demand of combined RCA-BEC circuit is additional and it consumes massive power consumption to perform 16-bit binary addition process. Hence, to cut back this problem, EHRCA circuit is meant during this paper. The transient description of EHRCA is bestowed in next section.

#### 5. Enhanced Half Ripple Carry Adder

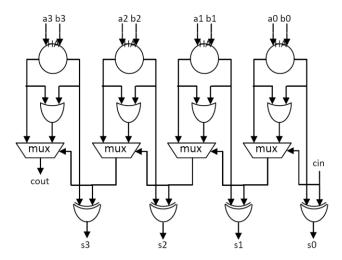

RCA is one of the simple adders to carry out the binary addition manner. However, CPD is the primary negative aspects in RCA circuit (i.e.,) each level ought to have anticipate bring sign from preceding level. In order to lessen the trouble of CPD in RCA circuit, Enhanced Half Ripple Carry Adder (EHRCA) is advanced in our work. The circuit diagram for advanced EHRCA circuit for 4-bit is illustrated in Figure 5. It includes HAs, OR gate, AND gate and Multiplexors for appearing addition manner. As the call itself, very last 1/2 of of the circuit best (Multiplexors part) ought to should wait till bring sign load from preceding level, ultimate circuits can execute in a parallel way. Hence, this adder circuit named as Enhanced Half Ripple Carry Adder. In different hand, the shape of this circuit is like that SQRT CSLA. Instead of RCA-BEC mixture for Cin = zero and Cin = 1 respectively of CSLA circuit, simplified circuit is designed as proven in Figure 5. The

Volume: 08 Issue: 06 | June 2021

www.irjet.net

bring enter is taken into consideration best very last level of EHRCA wherein as ultimate circuit can carry out the respective computation in a parallel way with the assist of to be had enter data. Similar to Figure 5, we will layout the EHRCA circuit for 8-bit and 16-bit. Further, the EHRCA adder is included into the addition manner of Equation (6) to boom the overall performance of 2-D DWT. Three tiers of decomposition are made on this paper for picture compression. The performances of traditional SQRT CSLA and advanced EHRCA circuits are analyzed in Results and Discussion of this paper.

Figure 5. Circuit diagram for 4-bit EHRCA circuit.

#### 6. Results and Discussions

In this paper, Enhanced Half Ripple Carry Adder (EHRCA) circuit is designed using Verilog Hardware Description Language (Verilog HDL). The validation of proposed adder circuit is evaluated using Model Sim 6.3C and Synthesis results are evaluated by using Xilinx 10.1i design tool. Also levels of decomposition of image using 2-D DWT are measured using MATLAB tool. The RCA circuit is realized in this paper and identified the redundant logic operations. Based on identified redundant logic, EHRCA circuit is designed in our work. The circuit of EHRCA is most likely conventional BEC based SQRT CSLA. Hence, the performance of conventional BEC based SQRT CSLA and developed EHRCA circuit for 16-bit is compared in Table 1.

SQRT CSLA and developed 16-bit EHRCA circuits

| Туре                | Slices | LUT | Delay(ns) | Power(mW) |

|---------------------|--------|-----|-----------|-----------|

| 16-bit Conventional |        |     |           |           |

| BEC based SQRT      | 28     | 47  | 15.971    | 280       |

| CSLA                |        |     |           |           |

| 16-bit developed    | 25     | 42  | 16.707    | 247       |

| EHRCA               | 25     | 42  | 10./0/    | 24/       |

Table 1. Comparison of 16-bit conventional BEC based

In this paper, Enhanced Half Ripple Carry Adder (EHRCA) circuit is meant the use of Verilog Hardware Description

Language (Verilog HDL). The validation of proposed adder circuit is evaluated the use of Model Sim 6.3C and Synthesis effects are evaluated with the aid of using the use of Xilinx 10.1i layout tool. Also ranges of decomposition of picture the use of 2-D DWT are measured the use of MATLAB tool. The RCA circuit is realized all through this paper and recognized redundant common the operations. supported recognized redundant common sense, EHRCA circuit is meant in our work. The circuit of EHRCA is presumably traditional BEC primarily based totally SQRT CSLA. Hence, the overall performance of traditional BEC primarily based totally SQRT CSLA and advanced EHRCA circuit for 16-bit is as compared in Table 1.From Table 1, its clean that 16-bit advanced EHRCA circuit gives 10.71% discount in silicon region and 11.78% discount in energy intake than traditional BEC primarily based totally SQRT CSLA. Therefore, advanced EHRCA circuit is that the maximum appropriate option for 2-D DWT implementation. Further, the advanced EHRCA circuit is integrated into 2-D DWT addition process to enhance the overall performance. The simulation end result for 2-D DWT is illustrated in Figure 6. The enter picture is transformed into the pixels and those pixels are confirmed in Figure 6. Three ranges of decomposition are made all through this paper for compression with the assistance of DWT and EHRCA. The enter picture for to be decide the DWT coefficients is proven in Figure 7. Three ranges of decomposed pix are illustrated in Figure 8.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Figure 6. Simulation result for image compression using 2-D DWT.

# International Research Journal of Engineering and Technology (IRJET)

IRIET Volume: 08 Issue: 06 | June 2021 www.irjet.net p-ISSN: 2395-0072

Figure 7. Input Image.

### Level 1 Level 2 Level 3

Figure 8. Three levels of decomposed images.

#### 7. Conclusion

In this 2-D primarily paper, totally compression is advanced with the assistance of Enhanced Half Ripple Carry Adder (EHRCA). the planning of EHRCA and incorporation of EHRCA into DWT computation is completed with the aid of using Verilog HDL. The advanced EHRCA circuit consumes much less hardware assets and energy intake than traditional BEC primarily based totally SQRT CSLA. The advanced EHRCA circuit gives 10.71% discount in silicon place and 11.78% discount in energy intake than traditional BEC primarily based totally SQRT CSLA. Further, advanced EHRCA circuit included into addition system of 2D-DWT for compression. Three degrees of decomposition are the duration of this paper. Simulation made for consequences for compression Figure 7. Input Image. Figure 8. Three degrees of decomposed images. the usage of 2-D DWT is tested with the aid of using each Model Sim

6.3C and MATLAB simulation tools. In future, the advanced EHRCA primarily based totally 2-D DWT are going to be useful for photo processing programs like compression, segmentation and fragmentations.

e-ISSN: 2395-0056

#### REFERENCES

- [1] Chao C, Parhi KK. High-speed VLSI implementations of 2-D discrete wavelet transform. IEEE Transactions on Signal Processing. 2008; 56(1):393–403.

- [2] Devangkumar S, Vithlani CH. VLSI-oriented lossy image compression approach using DA-based 2D-discrete wavelet. Int Arab J Inf Technol. 2014; 11(1):59–68.

- [3] Lee D-U, Kim L-K, Villasenor JD. Precision-aware self@quantizing hardware architectures for the discrete wavelet transform. IEEE Transactions on Image Processing. 2012; 21(2):768–77.

- [4] Manju P, Rohil H. Optimized image steganography using Discrete Wavelet Transform (DWT). IJRDET. 2014; 2(2):75–81.

- [5] Mohanty BK, Meher PK. Memory-efficient high-speed convolution-based generic structure for multilevel 2-D DWT. IEEE Transactions on Circuits and Systems for Video Technology. 2013; 23(2):353–63.

- [6] Monika R, Vij A. Image compression using discrete haar wavelet transforms. IJEIT. 2014; 3(12):47–51.

- [7] Nahvi N, Sharma OC. Implementation of discrete wavelet transform for multimodal medical image fusion. IJETAE. 2014; 4(7):312–7.

- [8] Nanammal V, Abirami BM, Venugopalakrishnan J. VLSI based desgin of an efficient hybrid water marking scheme for multimedia content protection. Indian Journal of Science and Technology. 2015; 8(19).

- [9] Vishwanath M, Michael RO, Irwin MJ. VLSI architectures for the discrete wavelet transform. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing. 1995; 42(5):305–16.

- [10] Zhang C, Wang C, Ahmad MO. A pipeline VLSI archi@tecture for fast computation of the 2-D discrete wavelet transform. IEEE Transactions on Circuits and Systems I: Regular Papers. 2012; 59(8):1775–85.