# MULTI LEVEL INVERTER FOR GRID CONNECTED SYSTEM

G. Satheesh Kumar<sup>1</sup>, K. Anitha<sup>2</sup>, N. Dharani<sup>3</sup>, J. Priyadharshini<sup>4</sup>, S. Vasim Akram<sup>5</sup>

Assistant Professor¹, Final Year Student² Department of Electrical and Electronics Engineering, SSM Institute of Engineering and Technology, Dindigul, Tamilnadu, India

**Abstract** - Multilevel inverters are among the most used power conversion devices in industrial applications. These applications mostly comprise of the motor drives for the entire voltage and power ratings. Multilevel inverters (MLIs) are also finding their applications in the gridconnected systems, uninterruptible power supply (UPS), electric vehicles and FACTS devices. All these applications are possible due to the ability of the MLI to provide a better output voltage with a more sinusoidal shaped waveform, improved efficiency due to the lower switching frequency operation of switches, lower blocking voltage requirement with reduced dv/dt and improved electromagnetic compatibility. Another positive impact of MLI is the reduction of the later size and cost due to the reduced amount of harmonics at the output. The conventional multilevel inverter topologies for the industrial application include neutral point clamped (NPC) MLI, laying capacitor (FC) MLI, cascade H-bridge (CHB) MLI, T-type MLI and modular multilevel converters (MMC). These MLI topologies have found their applications with different power and voltage ratings, along with their unique benefits as well as shortcomings. These shortcomings include the higher number of components for a higher number of levels along with capacitor voltage balancing problems.

*Key Words*: IGCTs, IGBTs, Rectifier, Regulator, Multilevel inverter, pwm.

### 1. INTRODUCTION

The main driving force for the design of new multilevel inverter topologies has been the reduction of the number of switches, number of dc voltage sources, and total standing voltage (TSV) of the topology. Based on these constraints, several topologies with reduced switch count have been pro-posed in the literature, such as in. All of them have used H-bridge in order to generate the positive and negative polarities of the output voltage waveform. However, the switches of H-bridge need to maximum/peak output Power converters, especially dc/ac PWM inverters have been extending their range of use in industry because they provide reduced energy consumption, better system efficiency, improved quality of product, good maintenance, and so on. In order to overcome these drawbacks, several new topologies for the multilevel inverter and their control have been introduced in.

#### 2. LITERATURE SURVEY

Ayoub Kavousi (2015) et al presents the Bee optimization method for harmonic elimination in a cascaded multilevel inverter. The main objective in selective harmonic elimination pulsewidth modulation strategy is eliminating low-order harmonics by solving nonlinear equations, while the fundamental component is satisfied. In this paper, the Bee algorithm (BA) is applied to a 7-level inverter for solving the equations. The algorithm is based on the food foraging behavior of a swarm of a honeybees and it performs a neighborhood search combined with a random search. This method has higher precision and probability of convergence than the genetic algorithm (GA).

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Mahrous Ahmed (2017) et al proposes a new method to calculate switching angles in selective harmonic elimination technique (SHE). It is introduced as a substitute for Newton-Raphson method and similar iteration methods. By utilizing classical control such as the proportional-integral (PI) control, the proposed method can perform a real-time calculation for multilevel inverter's (MLI) switching angles over a wide range of modulation indexes. Therefore, it is able to respond to system dynamics without the need to store pre-calculated large lookup tables.

Kehu Yang (2015) et al designed a user-friendly software package has been developed and some computation results are given. Unlike the commonly used numerical and intelligent methods, this method doesn't need to choose the initial values and can find all the solutions. Also, this method can give a definite answer to the question of whether the SHE equations have solutions or not, and the accuracy of the solved switching angles are much higher than that of the reference method.

# 3. PROPOSED SYSTEM

The voltage source inverters produce an output voltage or current with levels either 0 or ±Vdc. They are known as the two-level inverter. To produce a quality output voltage or a current wave form with less amount of ripple content, they require high switching frequency. In high- power and high voltage applications these two level inverters, however, have some limitations in operating at high frequency mainly due to switching losses and constraints of device ratings. These

© 2020, IRJET | Impact Factor value: 7.529 | ISO 9001:2008 Certified Journal | Page 5571

limitations can be overcome using multilevel inverters. There are 3 types of multilevel inverters named as diode clamped multilevel inverter, flying capacitor multilevel inverter and cascaded multilevel inverter. These three types of multilevel inverters requires more no. of components such as switches, clamping diodes and capacitors. As the number of voltage levels m grows the number of active switches increases according to 2×(m-1) for the cascaded H-bridge multilevel inverters. Multilevel inversion is a power conversion strategy in which the output voltage is obtained in steps thus bringing the output closer to a sine wave and reduces the total harmonic distortion (THD). This paper presents a 3-Φ seven level cascaded H-bridge multilevel inverter based on an MLDCL and a bridge inverter. Compared with the existing cascaded multilevel inverters, the proposed MLDCL inverter topologies can have enhanced performance by implementing the pulse width modulation (PWM) techniques. This paper also presents the most relevant control and modulation methods by a new reference/carrier based PWM scheme for MLDCL inverter and comparing the performance of the proposed scheme with that of the existing cascaded H-bridge multilevel inverter. The proposed MLDCL inverter can significantly reduce the switch count as well as the number of gate drivers as the number of voltage levels increases. For a given number of voltage levels m, the cascaded MLDCL inverter requires m+3 active switches, roughly half the number of switches.

### 4. HARDWARE

### 1) Power supply

There are many types of power supply. Most are designed to convert Voltage AC Mains electricity to a suitable low voltage supply for electronic Circuits and other Devices. A power supply can by broken down into a series of blocks, each of which performs a particular function.

Fig 1 Regulated Smoothing Regulator Rectifier Transforme 5V DC Block Diagram of a Regulated Power Supply System

The AC supply main is given to the step down transformer. The transformer having the different voltages. The output from the transformer is given to the rectifier circuit. In this rectifier circuit the AC voltage is converted to DC voltages. The rectified DC voltage is given to the regulator circuit. The output of the regulator is depends upon the regulator IC chosen in the circuit.

## 2) Bridge rectifier

A bridge rectifier can be made using four individual diodes, but it is also available in special packages containing the four diodes required. It is called a full-wave rectifier.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Smoothing is performed by a large value electrolytic capacitor connected across the DC Supply to act as a reservoir, supplying current to the output when the varying DC Voltage from the rectifier is falling.

### 3) Regulator

Voltage regulators ICs are available with fixed (typically 5, 12 and 15V) or variable Output voltages. They are also rated by the maximum current they can pass. Negative Voltage regulators are available, mainly for use in dual supplies. Most regulators include some automatic protection from excessive current ('overload protection') and Overheating ('thermal protection').

Fig2: Regulator

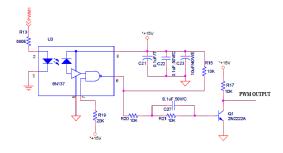

The function of the opto-isolator is to isolation between the power circuit and control circuit. In generally the control side power is less compared to the power circuit. For separating the high voltage side and the low voltage side the opto-isolator playing a major role. Normally the output of the opto-isolator is inverse of the input pulse. So in case of inverter circuits the output of the optoisolator is given to the transistors and again the signal will be inverted and given to the driver ic's.

Fig3: Opto isolator diagram

#### 5. CONCLUSION

A new cascaded multilevel inverter topology has been pro-posed in this paper with the advantage of having a reduced number of switching devices as well as number of dc voltage sources. The basic unit of the proposed topology generates 11 levels across the load employing eight switches with three dc voltage sources. Two different modes of dc voltage selection have also been presented for the generalized structure of the proposed

topology. Both of these modes reduce the need for a variety of dc voltage sources to only two, which makes the proposed topology more practical. To achieve more number of levels at the output, a detailed cascade connection of the proposed topology has been discussed. In a cascade connection, three different algorithms have been formulated in this paper to select the magnitude of the dc voltage sources. Furthermore, the optimization assessments of the cascade connections has been completed using all three algorithms. An in-depth comparison with other recently proposed optimal structure conforms the benefit of the proposed topology. The theoretical explanation of the proposed topology has been verified for the basic unit and cascade connection of two modules in the second algorithm using a laboratory prototype setup.

#### 6. REFERENCES

[1] H. Akagi, "Multilevel converters: Fundamental circuits and systems,"

Proc. IEEE, vol. 105, no. 11, pp. 20482065, Nov. 2017.

- [2] S. Kouro et al., "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 25532580, Aug. 2010.

- [3] M. Norambuena, J. Rodriguez, S. Kouro, and A. Rathore, "A novel mul-tilevel converter with reduced switch count for low and medium voltage applications," in Proc. IEEE Energy Convers. Congr. Expo. (ECCE), Cincinnati, OH, USA, Oct. 2017, pp. 52675272.

- [4] Z. Zheng, K. Wang, L. Xu, and Y. Li, "A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles," IEEE Trans. Power Electron., vol. 29, no. 7, pp. 35373546, Jul. 2014.

- [5] H. Abu-Rub, A. Lewicki, A. Iqbal, and J. Guzinski, ``Medium voltage drivesChallenges and requirements," in Proc. IEEE Int. Symp. Ind. Electron., Bari, Jul. 2010, pp. 13721377.

- [6] Q. A. Le and D.-C. Lee, "A novel six-level inverter topology for medium-voltage applications," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 71957203, Nov. 2016.

- [7] X. Yuan, "Derivation of voltage source multilevel converter topologies," IEEE Trans. Ind. Electron., vol. 64, no. 2, pp. 966976, Feb. 2017.

- [8] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," IEEE Trans. Power Electron., vol. 31, no. 1, pp. 135151, Jan. 2016.

- [9] M. A. Memon, S. Mekhilef, M. Mubin, and M. Aamir, "Selective harmonic elimination in inverters using bioinspired intelligent algorithms for renew- able energy

conversion applications: A review," Renew. Sustain. Energy Rev., vol. 82, pp. 22352253, Feb. 2018.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

- [10] J. Venkataramanaiah, Y. Suresh, and A. K. Panda, "A review on symmet-ric, asymmetric, hybrid and single DC sources based multilevel inverter topologies," Renew. Sustain. Energy Rev., vol. 76, pp. 788812, Sep. 2017. [11] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel DC voltage sources," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 26432650, Aug. 2010.

- [12] E. Babaei, S. Laali, and Z. Bayat, "A single-phase cascaded multi- level inverter based on a new basic unit with reduced number of power switches," IEEE Trans. Ind. Electron., vol. 62, no. 2, pp. 922929, Feb. 2015.

- [13] H. Samsami, A. Taheri, and R. Samanbakhsh, "New bidirectional multi-level inverter topology with staircase cascading for symmetric and asym- metric structures," IET Power Electron., vol. 10, no. 11, pp. 13151323, Sep.

- [14] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel con- verter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655667, Feb. 2012.

- [15] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, ``An envelope type (E-type) module: Asymmetric multilevel inverters with components," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 71487156, Nov. 2016.

- [16] E. Samadaei, A. Sheikholeslami, S. A. Gholamian, and J. Adabi, "A square T-type (ST-Type) module for asymmetrical multilevel inverters," IEEE Trans. Power Electron., vol. 33, no. 2, pp. 987996, Feb. 2018.

- [17] M. Saeedian, J. Adabi, and S. M. Hosseini, "Cascaded multilevel inverter based symmetricasymmetricDCsources with reduced number of components," IET Power Electron., vol. 10, no. 12, pp. 14681478, Oct. 2017.

- [18] E. Babaei, S. Laali, and S. Alilu, "Cascaded multilevel inverter with series connection of novel H-bridge basic units," IEEE Trans. Ind. Electron., vol. 61, no. 12, pp. 66646671, Dec. 2014.

- [19] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimal design of new cascaded switch-ladder multilevel inverter structure," IEEE Trans. Ind. Electron., vol. 64, no. 3, pp. 20722080, Mar. 2017.

- [20] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimization assessment of a new extended multilevel converter topology," IEEE Trans. Ind. Electron., vol. 64, no. 6, pp. 45304538, Jun. 2017.

[21] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi,

e-ISSN: 2395-0056

eral multilevel converter topology based on cascaded connection of sub- multilevel units with reduced switching components, DC sources, and blocked voltage

by switches," IEEE Trans. Ind. Electron., vol. 63, no. 11,

pp. 71577164, Nov. 2016.

``A new gen-

[22] R. S. Alishah, S. H. Hosseini, E. Babaei, M. Sabahi, and A. Z. Gharehkoushan, "Optimal design of new cascade multilevel converter topology based on series connection of extended sub-multilevel units," IET Power Electron., vol. 9, no. 7, pp. 13411349, Jun. 2016.

[23] A. K. Sadigh, M. Abarzadeh, K. A. Corzine, and V. Dargahi, "A new breed of optimized symmetrical and asymmetrical cascaded multilevel power converters," IEEE J. Emerg. Sel. Topics Power Electron., vol. 3, no. 4, pp. 11601170, Dec. 2015.

© 2020, IRJET | Impact Factor value: 7.529 | ISO 9001:2008 Certified Journal | Page 5574