# **Metastability Mitigation & Error Masking of High speed Flip-Flop**

Shweta Pathak<sup>1</sup>, Satyarth Tiwari<sup>2</sup>

<sup>1</sup>*MTech. Scholar Dept. VLSI Design RKDFCE Bhopal, M.P, India* <sup>2</sup>Asst.Professor VLSI Design RKDFCE Bhopal, M.P., India \*\*\*\_\_\_\_\_\_

ABSTRACT- Metastability events are commonplace in digital circuits, and synchronizers are vital to shield us from their lethal outcomes. Originally synchronizers had been vital whilst playing an asynchronous enter (that is, one synchronized with the clock enter so that might trade exactly while the pattern). Everything changes can easily be metastable. Switch its data enter at the equal time that the sampling edge of the clock and also you get Metastability. The indicators relative period of each cycle varies a little, and subsequently main to the metastability, close enough to every other switches. This aggregate of metastability with regular show gadgets, arise often. Recent semiconducting metallic oxide progress (CMOS) moreover it ends in unprecedented ranges of integration in virtual logic systems. Due to the propagation delay of the path and timing clock keep time configuration errors failure occurs in virtual circuits. The proposed flip flops take advantage of the idea of either delayed information or pulse primarily based method to stumble on timing errors. The timing violations are masked by means of passing direct facts instead of grasp latch output to slave latch. Simulation outcomes display that the proposed turn-flops lessen the mistake covering latency as much as 23% respectively in normal process corners and increase the powerful timing error monitoring window compared to country of the artwork metastable immune turn-flops [14]. The proposed flip-flops can be utilized in dynamic voltage and frequency

Kev Words: Metastability, SAFF, CMOS, flip-flop, synchronizing, PDFF, latch

## 1. INTRODUCTION

The motive of enforcing the setup and hold time situations on combinational paths is to constrain the entire of every turn-flop: to make sure that it's miles held solid for at the least (ts<sub>u</sub>) seconds before the clock part and that it remains strong for no much less than (th) seconds afterwards. By doing so, flip-flop outputs are guaranteed to behave in a predetermined manner: they transition to the logic stage of the input monotonically, with a nominal transition time and within a nominal clock-to-q postpone. These homes are vital for the design of deterministic synchronous structures.

## 2. PROPOSED WORK

In this paintings, we analyze the metastability of the flipflops in each qualitative and quantitative manners.

Because turn-flops may additionally have unsymmetrical 0-1 and 1-zero output delays, we are able to use faster or slower propagation delay to pick out the exclusive output transitions. For example the zero-1 output postpone of PDFF and 1-zero output postpone of SAFF will both be called the faster propagation postpone.

In part-brought about flip-flops, enter facts is captured with the aid of an intermediate essential node in the grasp level earlier than it's far propagated to the output thru the slave stage. When the turn-flop is running close to the metastable area, the rivalry at that node can also propagate to the output and cause metastability. For qualitative analysis, we cognizance on figuring out and studying the important node in each flip-flop structure that reasons contention and results in metastability.

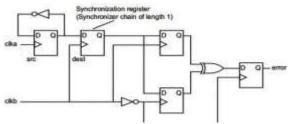

## 3. DESCRIPTION OF TEST CIRCUIT

The possibility of a latch to go into in a metastable nation is that when the most input signal ends with violates of installation time and keep time necessities. This is the case while the country of the D input of a flip-flop adjustments at every clock facet. Any other relationship among the frequency of the sign on the D enter and the clock frequency will reduce the probability of the latch that's to be examined enter a metastable state. The worst case is when the frequency  $(f_{in})$  on the D input is, precisely 1/2the clock frequency  $(f_{clk})$  (7).

Fig.1 Test Circuit Structure for Metastability Characterization

#### 4. FUNCTIONAL SIMULATION

Microwind helps all the front-end to lower backstop design go with the flow. For the frontend layout, we DSCH (digital schematic editor) who in-constructed ground simulator personal primarily based on virtual circuit. Users can also construct analog circuit and convert them into

e-ISSN: 2395-0056 p-ISSN: 2395-0072

**IRJET** Volume: 06 Issue: 06 | June 2019

www.irjet.net

documents and use third party simulators like Microwind or pspiceSPICE. DSCH can convert virtual circuit in the Verilog file can nevertheless by means of synthesized for FPGA/CPLD gadgets from any supplier. The identical Verilog record can be compiled for the conversion of setting Microwind. CMOS provisions may be verified the use of included blend sign simulator and in addition analysis for the DRC, delays, section 2D, 3D view, etc.

# 5. SIMULATION OF THE D-FLIP FLOP

Since our instance is a D flip-flop in uses factors of fantastic facet touchy garage, the Q output follows the D enter whilst the clock transitions from low to high, as indicated with the aid of the upward arrows inside the diagram above (7). There is not any doubt that the good judgment level is gift at the time of the clock due to the fact the date is stable earlier than and after the clock part. This is rarely the case in the shift registers with numerous flooring. But it became a easy example first of all. We are only involved approximately the tremendous, of low to high clock part. Negative facet can be not noted. It is very smooth to peer Q follow D at the clock above. Compare this to the Fig. Under For quantitative evaluation, the  $\tau$  and the calculated metastability window ( $\delta$ ) values of the turnflops are as compared in keeping with their faster and slower output propagation delays.

Figure 2 CMOS design basic d flip-flop

Figure 3 basic flip-flop voltage vs time

Figure 4 CMOS design metastabality of basic flip-flop

Figure 5 metastabality of basic flip-flop voltage vs time

Figure 6 CMOS design metastabality of proposed flip-flop voltage

Figure 7 metastabality of proposed flip-flop voltage vs time

International Research Journal of Engineering and Technology (IRJET) e-ISS

IRJET Volume: 06 Issue: 06 | June 2019

www.irjet.net

| parameter          | Power<br>dissipation | Clock<br>frequency | Number<br>of | Metastable<br>error |

|--------------------|----------------------|--------------------|--------------|---------------------|

|                    |                      |                    | transistor   |                     |

| proposed           | 2.577 uW             | 1.7Ghz             | 22           | 10                  |

| G.Sannena<br>et al | 372.4 uW             | 500 Mhz            | 50           | 11                  |

|                    |                      |                    |              |                     |

The paintings which has been proven in the Fig.6 suggests the metastable errors 10 compared with the paintings achieved within the preceding given paintings is tons more better performance as it offers us the mistake is 10 but formerly it changed into eleven to forty nine. There is lot of distinction between the electricity dissipation and switching delay.

The energy dissipation affects the circuit overall performance degradation which represents the Metastability delay. With the usage of transmission gate that reduces the stray capacitances and number of transistor requires designing the flip-flop circuit. The reduction in stray capacitances improves the postpone and strength dissipation in circuit. The performance of metastability robustness in 45 nm turn-turn is tested and a metastability occasions testing circuit is designed. Using faster the flip-flops decreases the setup and maintain instances of the turn-flop, which in flip decreases the time window that the flip-flop is prone to metastability while the input frequency is decreases, the probabilities of the input converting during the setup and keep time additionally decreases. Our circuit count metastable occasion and tolerate metastability is upload one or extra successive synchronizing flipflop to synchronize

# 6. CONCLUSION

The strength dissipation impacts the circuit performance degradation which represents the Metastability put off. With the usage of transmission gate that reduces the stray capacitances and quantity of transistor requires designing the turn-flop circuit. The reduction in stray capacitances improves the put off and strength dissipation in circuit. The overall performance of metastability robustness in 90 nm flip-flip is tested and a metastability activities checking out circuit is designed. Using faster the flip-flops decreases the setup and maintain times of the turn-flop, which in turn decreases the time window that the turn-flop is susceptible to metastability whilst the input frequency is decreases, the chances of the input changing at some stage in the setup and preserve time also decreases. Our circuit remember metastable event and tolerate metastability is upload one or greater successive synchronizing flipflop to synchronize.

An efficient approach to lessen the worst case timing shield bands using an errors masking flip-flop is mentioned. In this technique, an mistakes sign is flagged via errors covering turn-flop in case of timing violations. Clock gating controller makes use of this mistake sign to shift the fantastic fringe of the clock with the aid of one cycle to recover from timing violations. The proposed flipflop is proof against statistics route metastability and does no longer need a metastable detector. Exhaustive simulations were performed to validate the proposed timing error protecting scheme in both turn-flop and block ranges. The proposed flip-flop reduce the mistake overlaying latency via 16% in comparison to standard approach to be had in literature.

# 7. FUTURE SCOPE

There are several approaches to extend our paintings to accommodate emerging issues in circuit reliability. First, we advise to keep tackling the imperative trouble of enhancing the scalability of precise reliability computations, the usage of side-valued decision diagrams. Next, we endorse to enhance the SER of sequential circuits by way of taking benefit of the elevated resynthesis possibilities to be had

## 8. REFERENCES

[1] D. Ernst, N.S. Kim, S. Das, S. Pant, R. Rao, T. Pham, C. Ziesler, D. Blaauw, T.

Austin, K. Flautner, T. Mudge, B. Ave, A. Arbor, Razor: a lowpower pipeline based on circuit-level timing speculation, in: Proceedings of International Symposium on Microarchitecture, 2003, pp. 7–18.

[2] S. Das, D. Roberts, S. Lee, S. Pant, D. Blaauw, T. Austin, T. Mudge, K. Flautner, A self-tuning DVS processor using delayerror detection and correction, IEEE J.

Solid-State Circuits 41 (4) (2006) 792–804.

[3] S. Das, C. Tokunaga, S. Pant, W. Ma, S. Kalaiselvan, K. Lai, D.M. Bull, D.T. Blaauw, RazorII: in situ error detection and correction for PVT and SER tolerance, IEEE J.

Solid-State Circuits 44 (1) (2009) 32–48.

[4] K.A. Bowman, J.W. Tschanz, S.L.L. Lu, P.A. Aseron, M.M. Khellah,

A. Raychowdhury, B.M. Geuskens, C. Tokunaga, C.B. Wilkerson, T. Karnik, V. K.

De, A 45 nm resilient microprocessor core for dynamic variation tolerance, IEEE J. Solid-State Circuits 46 (1) (2011) 194–208.

[5] I. Kwon, S. Kim, D. Fick, M. Kim, Y. Chen, D. Sylvester, Razor-lite: a light-weight register for error detection by observing virtual supply rails, IEEE J. Solid-State Circuits 49 (9) (2014) 2054–2066.

[6] M. Fojtik, D. Fick, Y. Kim, N. Pinckney, D.M. Harris, D. Blaauw, D. Sylvester, Bubble Razor: eliminating timing margins in an ARM cortex-M3 Processor in 45 nm CMOS using architecturally independent error detection and correction, IEEE J. Solid-State Circuits 48 (1) (2013) 66–81.

[7] I. Shin, J. Kim, Y. Shin, Aggressive voltage scaling through fast correction of multiple errors with seamless pipeline operation, IEEE Trans. Circuits Syst. I Regul. Pap. 62 (2) (2015) 468–477.

[8] H. Fuketa, M. Hashimoto, Y. Mitsuyama, T. Onoye, Adaptive performance compensation with in-situ timing error b International Research Journal of Engineering and Technology (IRJET)  $\,$  e

**IRJET** Volume: 06 Issue: 06 | June 2019

www.irjet.net

predictive sensors for subthreshold circuits, IEEE Trans. Very Large Scale Integr. Syst. 20 (2) (2012) 333–343.

[9] B.P. Das, H. Onodera, Frequency independent warning detection sequential for dynamic voltage and frequency scaling in ASICs, IEEE Trans. Very Large Scale Integr. Syst. 22 (12) (2014) 2535–2548.

[10] V. Huard, F. Cacho, F. Giner, M. Saliva, A. Benhassain, D. Patel, N. Torres, S. Naudet, A. Jain, C. Parthasarathy, Adaptive wearout management with in-situ aging monitors, in: Proceedings of IEEE International Reliability Physics Symposium, 2014, pp. 1–11.

[11] Martin Omana, Daniele Rossi, Nicolo Bosio, Cecilia Metra, Low cost NBTI degradation detection and masking approaches, IEEE Trans. Comput. 62 (3) (2013) 496–509.

[12] B.P. Das, H. Onodera, Warning prediction sequential for transient error prevention, in: Proceedings of IEEE International Symposium DFT VLSI System, 2010, pp. 382–390.

[13] Govinda Sannena, B.P. Das, Area and Power-Efficient Timing Error Predictor for Dynamic Voltage and Frequency Scaling Application. in: Proceedings of IEEE International Symposium on Nanoelectronic and Information Systems, 2016, pp. 244–249.

[14] K. Chae, S. Mukhopadhyay, A dynamic timing error prevention technique in pipelines with time borrowing and clock stretching, IEEE Trans. Circuits Syst. I Regul. Pap. 61 (1) (2014) 74–83.

[15] K.Chae, Chang-Ho Lee, S. Mukhopadhyay, Timing error prevention using elastic clocking, in: Proceedings of IC Design and Technology, 2011, pp. 1–4.

[16] K. Chae, S. Mukhopadhyay, Resilient pipeline under supply noise with programmable time borrowing and delayed clock gating, IEEE Trans. Circuits Syst. II Express Briefs 61 (3) (2014) 173–177.