Volume: 05 Issue: 06 | June-2018

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

# DEVELOPMENT AND TESTING OF VHDL INTERFACES FOR HIGH SPEED MEMORY BUFFERING AND DATA TRANSMISSION ON FPGA DEVELOPMENT KIT FOR HIGH SPEED DIGITIZER

## Pragati Gupta, Vikas Kumar Rai

<sup>1</sup>Student, Dept. of Electronics and communication, SIT, Mathura, India <sup>2</sup>Associate Professor, Dept. of Electronics and communication, SIT, Mathura, India

**Abstract** - High speed physics experiments involve data acquisition and transmission from large number of channels. Transmission of huge amount of data within a short period of time is a demand of today's world. This paper deals with the development of VHDL interfaces for high speed memory buffering and data transmission. High speed digitizers sample and digitize analog signals upto 250 MSPS (mega samples per second). ADC data is processed using suitable signal processing algorithm. In order to achieve the high data throughput, memory buffering is used. Processed data is transferred over communication channel using PCI express. This paper deals with the High speed data transfer at 400 MHz clock on DDR3 memory.

Key Words: External memory interface, qsys(quartus system integration tool), DMA controller, Avalon interfaces, Memory buffering.

#### 1. INTRODUCTION

High speed digitizers produce large amount of data during data acquisition. Online digital data processing algorithms requires large amount of data to be buffered till the processing is being carried out. Processed data has to be transmitted to Data Archiving PC. In order to achieve the high data throughput, memory buffering is used. The scope of this paper is to transfer (read/write) the high speed data at 400Mhz clock on DDR3 SDRAM. This data is transferred over communication channel using PCI express.[5]

## 1.1 Cyclone V FPGA DEVICE:

The Cyclone V GT FPGA development board provides a hardware platform for developing and prototyping low-power, highperformance, and logic-intensive designs using Cyclone V GT FPGA device. The board provides a wide range of peripherals and memory interfaces to facilitate the development of Cyclone V GT designs. Design advancements and innovations, such as the PCI Express hard IP, partial reconfiguration, and hard memory [1]controller implementation ensure that designs implemented in the Cyclone V GTs operate faster, with lower power.

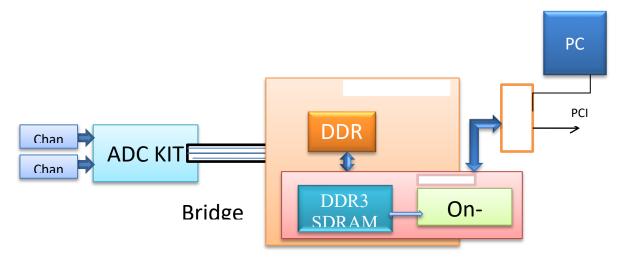

Fig -1: Block Diagram of the device

Volume: 05 Issue: 06 | June-2018 www.irjet.net p-ISSN: 2395-0072

e-ISSN: 2395-0056

#### 1.2 EXTERNAL MEMORY INTERFACE:

DDR3 SDRAM is the third generation of SDRAM. DDR3 SDRAM is internally configured as an eight-bank DRAM and uses an 8n pre-fetch architecture to achieve high-speed operation. The 8n pre-fetch architecture is combined with an interface that transfers two data words per clock cycle at the I/O pins. A single read or write operation for DDR3 SDRAM consists of a single 8n-bit wide, one-clock-cycle data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.[4]

UNIPHY: It is a physical layer of the external memory interface. It converts the double data rate interface of high speed memory devices to a full rate or half rate interface for use within an FPGA.

#### 1.3 Avalon Interface specifications:

Avalon interfaces simplify the system design by allowing to easily connection in the components in FPGA. The Avalon interface family define interfaces appropriate for streaming high speed data, reading and writing registers and memory, and controlling off-chip devices. System interconnect is a high-bandwidth structure for connecting components, and that allows us to connect IP cores to other IP cores with various interfaces. [8] We are using Avalon streaming interface, Avalon memory mapped interface and Avalon conduit interface, Avalon clock and Avalon reset interface.

#### 1.4 DMA Controller:

The direct memory access (DMA) controller core with Avalon interface performs bulk data transfers, reading data from a source address range and writing the data to a different address range. An Avalon Memory-Mapped (Avalon-MM) master peripheral, such as a CPU, can offload memory transfer tasks to the DMA controller. While the DMA controller performs memory transfers, the master is free to perform other tasks in parallel. [4]

The DMA controller transfers data as efficiently as possible, reading and writing data at the maximum pace allowed by the source or destination. The DMA controller is capable of performing Avalon transfers with flow control, enabling it to automatically transfer data to or from a slow peripheral with flow control (for example, UART), at the maximum pace allowed by the peripheral.

## 1.5 Memory buffering:

A memory buffer register (MBR) or memory data register (MDR) is the register in a computer's processor, or central processing unit, CPU, that stores the data being transferred to and from the immediate access storage. It contains the copy of designated memory locations specified by the memory address register. It acts as a buffer allowing the processor and memory units to act independently without being affected by minor differences in operation.[6] A data item will be copied to the MBR ready for use at the next clock cycle, when it can be either used by the processor for reading or writing or stored in main memory after being written.

This register holds the contents of the memory which are to be transferred from memory to other components or vice versa. A word to be stored must be transferred to the MBR, from where it goes to the specific memory location, and the arithmetic data to be processed in the ALU first goes to MBR and then to accumulated register, and then it is processed in the ALU.

#### 2. READ/WRITE DDR3 SDRAM:

Here, we are reading and writing the DDR3 SDRAM by giving the software commands in the NIOS Embedded design suite using the Eclipse processor.

There are following components required in our NIOS system-

- Clock.

- DDR3 SDRAM controller with UniPHY.

- Nios II processor.

- On-chip memory.

- JTAG UART.

After creating a qsys system design and instantiation in the Quartus, pin assignment is performed to connect the design to the hardware for the proper read/write of SDRAM.

Volume: 05 Issue: 06 | June-2018

www.irjet.net

e-ISSN: 2395-0056

p-ISSN: 2395-0072

For the configuration of the FPGA we have programmed our design on the FPGA design toolkit using the programmer. The sof file which contains the hardware design is programmed on FPGA. Writing a software program in eclipse tool to write/read DDR3 SDRAM[6]

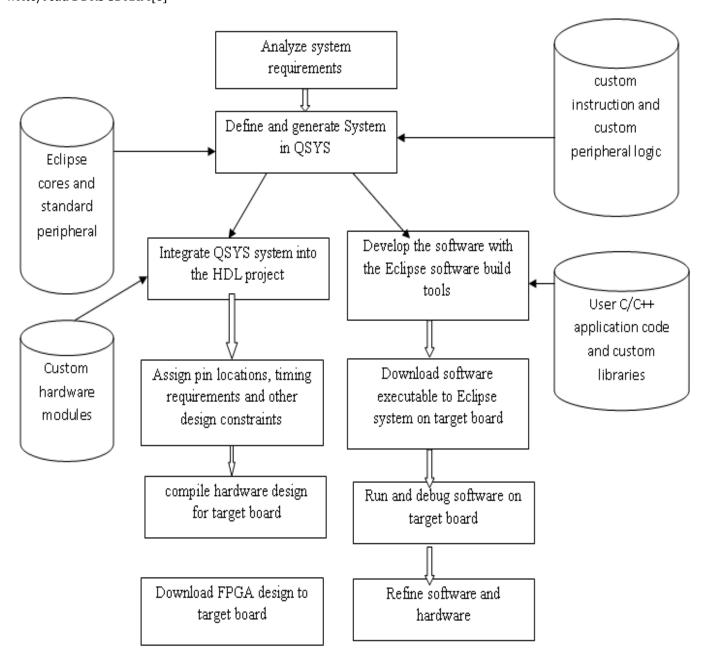

Chart -1: Eclipse EDS system development flow.

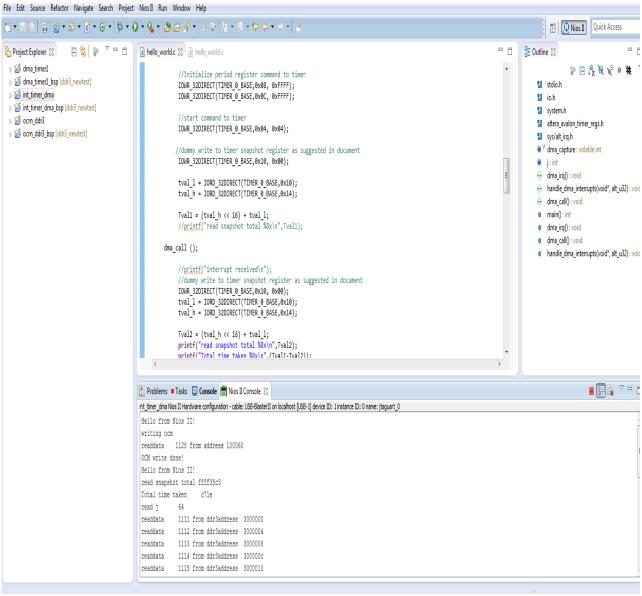

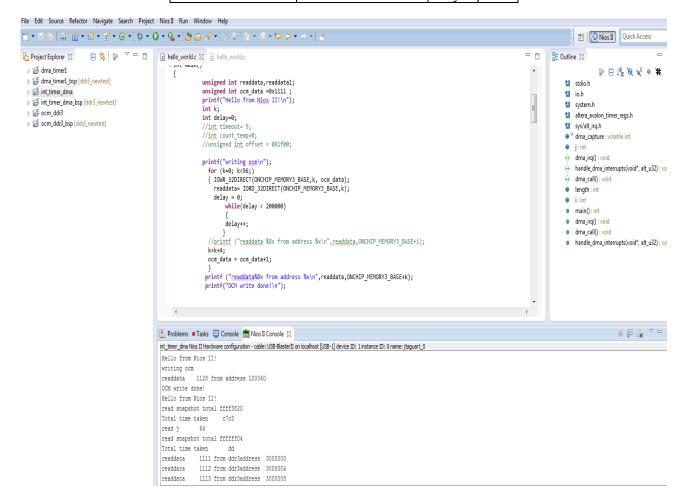

Using the eclipse NIOS tool we can easily communicate with the device for the efficient transfer of the data. Here, Chart 1 shows the development flow of eclipse NIOS II tool. After creating a new project in the embedded design suite processor, we created a software program and generated the board support package (BSP) file. We are accessing the DDR3 by writing and reading to some specific addresses by giving the commands in the EDS processor. Figure 2 shows the Eclipse console window for DDR3 read/write on specified addresses.[7]

Volume: 05 Issue: 06 | June-2018

www.irjet.net

File Edit Source Refactor Navigate Search Project Nios II Run Window Help Project Explorer 🔀 🔝 hello\_world.c 🔀 ⊕ \* "Hello World" example... b hlw\_sai\_bsp [ddr3\_newtest] #include <stdio.h> #include <io.h> p mem\_test\_bsp [ddr3\_newtest] #include <system.h> b p mem testsmall int main() unsigned int readdata; ⊳ 📂 RDWR printf("Hello from Nios II!\n"); IOWR\_32DIRECT(MEM\_IF\_DDR3\_EMIF\_0\_BASE, 0x01, 0xf1234567); readdata= IORD\_32DIRECT(MEM\_IF\_DDR3\_EMIF\_0\_BASE, 0x01); printf ("read data %8x\n", readdata); IOWR\_32DIRECT(MEM\_IF\_DDR3\_EMIF\_0\_BASE, 0x02, 0xf1234666); readdata= IORD\_32DIRECT(MEM\_IF\_DDR3\_EMIF\_0\_BASE, 0x02); printf ("read data %8x\n", readdata); IOWR\_32DIRECT(MEM\_IF\_DDR3\_EMIF\_0\_BASE, 0x03, 0xf1234555); 🖳 Problems 🔳 Tasks 📮 Console 🛗 Nios II Console 🛭 🔳 Properties RDWR Nios II Hardware configuration - cable: USB-BlasterII on localhost [USB-1] device ID: 1 instance ID: 0 name: jtaguart\_0 Hello from Nios IIIII! writing ocm readdata f1111111 from address 0 readdata f1111111 from address 4 readdata f1111111 from address 8 readdata f1111111 from address readdata f1111111 from address readdata f1111111 from address 14 readdata f1111111 from address readdata f1111111 from address writing ddr3 readdata f2222222 from address 2000000 readdata f2222222 from address 2000004 readdata f2222222 from address 2000008 readdata f2222222 from address 200000c readdata f2222222 from address 2000010 readdata f2222222 from address 2000014 readdata f2222222 from address 2000018 readdata f2222222 from address 200001c readdata f2222222 from address 2000020

**Fig -2:** Eclipse console window showing DDR3 read/write on specified addresses.

#### 3. Throughput analysis of DDR3 SDRAM Controller:

We are designing a system to transfer the data in between the on-chip memory and the DDR3 SDRAM controller. Firstly, we write our data on the on-chip memory.

Secondly, we initialized our DMA Controller by giving the read address (address of the memory from which the data is to be read), write address (address of the memory from which the data is to be write), DMA transaction length (in bytes), status register and control port register. In our case the reading memory is on-chip memory and the writing memory is DDR3 SDRAM. After writing the control port command our data is transferred directly from on-chip memory to the DDR3 SDRAM.

Thirdly, reading and printing the data from DDR3 SDRAM serially.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Volume: 05 Issue: 06 | June-2018

www.irjet.net

File Edit System Generate View Tools Help 💢 System Contents 🔞 Address Map 🔞 Interconnect Requirements 🗯 IP Catalog 83 - 리 ㅁ – ਰੰ⊏ System: ddr3\_newtest Path: dma\_0 × IRQ Tag: Project mp white clk 1 Clock Input clk U New Component. mp\_wfifo\_reset\_n\_1 Reset Input Double-click to export ...System Library csr\_dk Clock Input **7** Basic Functions csr\_reset\_i Reset Input ⊕ DSP I -0status Conduit status -0oct Conduit oct Low Power pll sharing Conduit 7 On-Chip Memory (RAM or ROM) ☐ onchip\_memory2\_0 ¥ Processors and Peripherals Clock Input - Osvs Interconnect s1 Avalon Memory 0x0000\_0000 -University Program reset1 Reset Input [dk1] 7 □ III nios2\_gen2\_0 Nios II Processo dk Clock Input clk 0 Reset Input [dk] reset data\_master Avalon Memory Mapped Master Double-click to export instruction\_maste Avalon Memory Mapped Maste New... Edit... ♣ Add. Double-click to export irq Interrupt Receiver [clk] IRO IRO 31 debug\_reset\_request Reset Output [dk] Hierarc 🛭 Device Fan 🕮 \_ f<sup>†</sup> □ debug mem slave Avalon Memory Mapped Slave [dk] 0x0408 0800 0x0408 Offf )--**:[]:** dma\_ custom\_instruction\_master Custom Instruction Master }-**:□** jtag\_uart\_0 }-**:□** mem\_if\_ddr3\_emif\_0 7 JTAG UART ☐ jtag\_uart\_0 Clock Input ... **a**fidk Reset Input [dk] ⊕ **- a**fi\_half\_clk 0x0408 1048 avalon\_jtag\_slave Avalon Memory Mapped Slave [dk] 0x0408 104f ira Interrupt Sender [dk] ... **►** avl\_0 dk Clock Input clk 0 ± - csr dk ⊕ **b** csr\_reset\_n Reset Input Double-click to export [dk] reset Double-click to export control\_port\_slave Avalon Memory Mapped Slav [dk] 0x0408\_1020 x0408\_103f ⊕ memory Interrunt Sender [dk] ira ⊕ - mp cmd dk 0 read maste Avalon Memory Mapped Maste [dk] write\_master Avalon Memory Mapped Maste ⊕ **p** mp\_rfifo\_dk\_1 ⊞ mp rfifo reset n 0 🞶 🏦 🔻 🗑 Current filter. ⊞ - mp wfifo dk 0 \_ ਜੰ □ → mp\_wfifo\_clk\_1 0 Errors, 5 Warnings

Fig -3: Complete QSYS design for the transfer of data through DMA controller.

We have successfully transferred our data through DMA between the memories as shown in the figure 4 the console is showing the read-data that is transferred in the DDR3 SDRAM. The main objective is to find the time taken in the transfer of the data between the On-chip memory and the DDR3 SDRAM.

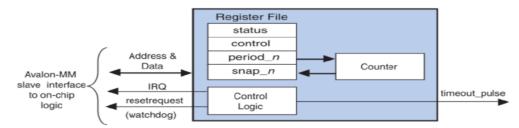

Fig -4: Interval timer core block diagram.

For the calculation, the time of the transfer we are using the interval timer in our design. There are following steps used in

- 1. Adding timer in the system integration tool of our later design. Initialization of the parameters for the interval timer.

- 2. Generation of the design and then integrating the QSYS design with the System design tool project.

- 3. Simulation and compilation of the final design.

- 3. Programming the design on the programmer.

- 4. Initializing the timer before the DMA controller control port command in embedded design suite processor.

- 5. Reading the counter snapshot before and after the transfer. This Timer works in countdown mode already.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Volume: 05 Issue: 06 | June-2018

www.irjet.net

e-ISSN: 2395-0056

p-ISSN: 2395-0072

File Edit Source Refactor Navigate Search Project Nios II Run Window Help Nios II Ouick Acce - E Project Explorer 🛭 lc hello\_world.c ⋈ lh system.h □ Outline 🛭 ⊳ 👺 ocm\_ddr3 P □ 1 N N A//checking length stdio.h ⊳ 📂 RDWR u io.h → BRDWR\_bsp [ddr3\_newtest]

→ BRDWR\_bsp [ddr3\_newtest 🦹 Problems 🔳 Tasks 📮 Console 🧂 Nios II Console 🛭 🗷 Properties ocm\_ddr3 Nios II Hardware configuration - cable: USB-BlasterII on localhost [USB-1] device ID: 1 instance ID: 0 name: jtaguart\_0 Hello from Nios II! writing ocm readdata 1128 from address 4090060 OCM write done! read dma 4090000 read dma 2000000 read dma Λ read dma 8c read dma command to dma is given! read dma status reg dma transfer done dma transfer is OVER 1111 from ddr3address 2000000 readdata 1112 from ddr3address 2000004 readdata readdata 1113 from ddr3address 2000008 1114 from ddr3address 200000c readdata 1115 from ddr3address 2000010 readdata readdata 1116 from ddr3address 2000014 1117 from ddr3address 2000018 readdata readdata 1118 from ddr3address 200001c readdata 1119 from ddr3address 2000020 111a from ddr3address 2000024 readdata 111b from ddr3address 2000028 readdata readdata 111c from ddr3address 200002c 111d from ddr3address 2000030 readdata

Fig -5: Data transfer from On-chip memory to DDR3 through DMA Controller.

We are writing interrupt service routine (ISR) for the DMA Controller to put the status register zero after each DMA transfer cycle completes to start new transfer again. Software often communicates with peripheral devices using interrupts. When a peripheral asserts its IRQ, it causes an exception to the processor's normal execution flow. When such an IRQ occurs, an appropriate ISR must handle this interrupt and return the processor to its pre-interrupt state upon completion. We are calling the alt\_irq\_register() function, which enables the interrupts.

DMA controller can signal an interrupt request (IRQ) when a DMA transaction completes. DMA transaction proceeds as follows:

- 1. CPU prepares the DMA controller for a transaction by writing to the control port that transaction is starting.

- 2. The CPU enables the DMA controller. The DMA controller then begins transferring of data between the on-chip memory and DDR3 SDRAM without additional intervention from the CPU. The DMA's master read port reads data from the read address which is OCM. The master write port writes the data to the destination address, which is DDR3 SDRAM. A shallow FIFO buffers data between the read and write ports.

- 3. The DMA transaction ends when a specified number of bytes are transferred (a fixed-length transaction) or an end-of-packet signal is asserted. At the end of the transaction, the DMA controller generates an interrupt request (IRQ).

- 4. The DMA controller has a single IRQ output that is asserted when the status register's DONE bit equals 1 and the control register's I\_EN (Enables interrupt requests) bit equals 1.

Volume: 05 Issue: 06 | June-2018

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

5. During or after the transaction, the CPU can determine if a transaction is in progress, or if the transaction ended (and how) by examining the DMA controller's status register. Writing the status register clears the DONE bit and acknowledges the IRQ. We can also read the status register to cross-check our transaction.

The transaction can be burst or the normal mode. In burst transfer mode, the DMA controller performs the burst transactions on its master read and write mode. Maximum burst transaction of DMA controller is 1024 words. We are reading the timer snapshot before and after the transfer.

#### 3. CONCLUSIONS

We can find out the transfer time taken by DMA controller using a timer. Every transferring of data takes a different period of time because of the delay in the processing. We can calculate an average time of the transfer. We have calculated time of the transfer in two different modes, the burst mode and the normal mode.

Although, the time calculated in two different modes is approximately same. The figure 6 and figure 7 shows the DMA transfer time in two different modes.

Fig -6: DMA transfer in burst mode.

The estimated theoretical time calculated is 508 us, and we can see our result is nearly to this value. We have calculated the time taken by the commands in one DMA transfer that is equal to 2.20 us in burst mode. By that we can calculate the

Volume: 05 Issue: 06 | June-2018

www.irjet.net

transfer time taken in 100 times running of DMA transfer commands as the DMA initialization commands is also taking some unit of time in processing. And the rest of the time is taken by the DMA controller in the actual DMA transfer between the On-chip memory and DDR3 SDRAM. We can calculate the throughput of our transfer process.

**Table 1**: Controller transfer timings in burst mode.

| Average time in<br>DMA transfer | Avg. time taken by<br>the commands of<br>DMA controller for<br>100times<br>initialization | Throughput<br>obtained |

|---------------------------------|-------------------------------------------------------------------------------------------|------------------------|

| 510.12 us                       | 220 us                                                                                    | 196<br>Mbytes/sec      |

Fig -7: DMA transfer in normal mode.

**Table 2:** Controller transfer timings in normal mode.

| Average time in<br>DMA transfer | Avg. time taken by<br>the commands of<br>DMA controller for<br>100times<br>initialization | Throughput obtained |

|---------------------------------|-------------------------------------------------------------------------------------------|---------------------|

| 511.17 us                       | 227 us                                                                                    | 195<br>Mbytes/sec   |

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Volume: 05 Issue: 06 | June-2018

www.irjet.net

e-ISSN: 2395-0056

p-ISSN: 2395-0072

To transfer the high speed data, we need data buffering in order to achieve the high data throughput. This work results the transfer (read/write) of the high speed data at 400Mhz clock on DDR3 SDRAM. The transfer speed is very fast because the DMA controller doesn't occupy the CPU in the processing. The average time of DMA controller in 100 times transferring of 1 Kbyte of data is 510 us. The throughput obtained by transferring 100Kbytes of data is 196 Mbytes/sec. This data is further transferred over communication channel using PCI express.[3]

#### 4. SUMMARY AND FUTURE SCOPE

In the present work we are transferring our data on a clock of 400Mhz on the DDR3 SDRAM. We can transfer this data on higher clock frequency. Throughput can be increased by using efficient memory buffering technique. This work is proposed to be used in data acquisition system for the accelerator which would collect data from the detectors which will be sending over the high speed interfaces as PCI express. This analog data from detector is digitized using ADC, which generate output data of 2Gbps.

So, the next target of this work is to transmit the data at high speed (2Gbps or more) from the DDR3 SDRAM depending on the trigger condition to the PCI Express. This will reduce the hardware requirement and increase the throughput and reliability of the system.

#### REFERENCES

- [1] Reference Manual: Altera Cyclone V GT FPGA Development Board, Jan 2015.

- [2] Internetworking Technology Overview, University of St. Andrews, June 1999

- [3] User Guide: Triple-Speed Ethernet MegaCore Function, Corporation.

- [4] Quartus Sytem Design Handbook: Corporation, Jun 2014.

- [5] Tom Shanley, Ravi Budruk, and Don Anderson, "PCI Express System Architecture," Mindshare, Addison-Wesley publishing company, 2003.

- [6] Altera Reference Manual: External memory interface handbook, corporation, Sept 2016.

- [7] Bhasker, J., A VHDL Synthesis Primer, Allentown, PA: Star Galaxy Publishing, 1995.

- [8] San Jose, "Avalon Interface Specifications", 101 Innovation Drive, Software Version 13.1, December 2013.