IRIET

# A survey on architectural modifications for improving performances of devices using FINFET techniques

## M.Susaritha<sup>1</sup>, J.Senthil Kumar<sup>2</sup>, S.Vijavalakshmi<sup>3</sup>

<sup>1</sup>Assistant Professor, Dept. of Electronics and Communication Engg, Sona college of Technology, Tamilnadu, India <sup>2</sup> Professor, Dept. of Information Technology, Sona college of Technology, Tamilnadu, India.

<sup>3</sup> Assistant Professor, Dept. of Electronics and Communication Engg, Sona college of Technology, Tamilnadu, India \*\*\*\_\_\_\_\_

**Abstract -** This survey paper presents the analysis of FinFET (Fin-type Field-Effect Transistors) based on their performances. FinFETs are promising substitutes for bulk complementary metal oxide semiconductor beyond 22nm level. FinFETs are dual-gate devices. The two gates of a FinFET can either be connected together or independently controlled for lower leakage or reduced transistor count. The main objective of this survey is to make engineers and researchers to get benefited into the techniques for civilizing performances in terms of power, speed and area and motivate them to develop good solutions for enabling low-power process.

Key Words: body effect, soft error, process variation control, Read Static Noise Margin (RSNM), Asymmetric gate work function.

#### **1. INTRODUCTION**

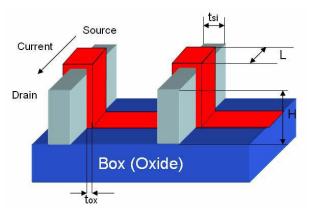

The FinFET device consists of a thin silicon body, the thickness of which is denoted by  $t_{si}$ , enclosed by gate electrodes. The direction of current flow is parallel to the wafer plane, here the channel is formed which is perpendicular to the plane of the wafer. Due to this reason. the device is termed quasi-planar [1]. Figure 1 gives you an idea about the design of a multi-fin FinFET.

Fig.1 multi-fin FinFET

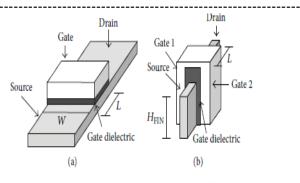

Fig.2.a) shorted gate b) independent gate

In shorted-gate (SG) FinFETs, both the gates are combined together, form a three-terminal device. This device can serve as a direct substitute for the conventional bulk-CMOS devices. In Independent-Gate (IG) FinFETs, the two gates are not connected together, it can be controlled separately [1]. E.J.Nowak et al.[2] have presented paper on double gate CMOS/FinFET Technology which describes FinFET device only sub threshold drain to source tunneling is significant while gate oxide tunneling and drain/source to body conduction are substantially reduced.

### **1.1 REDUCTION OF SHORT CHANNEL EFFECTS USING FinFETs**

FinFETs gives better manage of short-channel effects and also promising alternative for the 22nm technology node and beyond. The lightly doped channel of FinFET improves its resistance to process variations [2]. If FinFET back gate is reverse biased, it increases the threshold voltage (V<sub>th</sub>) of front gate, thus reducing leakage at the rate of increased delay [3].If FinFET back gate is reverse biased, it increases the V<sub>th</sub> of front gate, thus reducing leakage at the expense of increased delay. Unlike planner devices, a FinFET does not suffer from random do pant fluctuations due to its lightly doped channel. And also variations in the work functions of an n-FinFET &p-FinFET alter the V<sub>th</sub>. The ratio between the leakage & dynamic power of a circuit can vary drastically depending on the operating temperature [4]. The slew rate of op-amp is significantly improved 273 to 5590 v/ $\mu$ s using FinFET & operational Tran's conductance amplifier. The gain and phase margin remain unchanged [6].Double Gate (DG)

MOSFET is to be the best for the device down scaling as it allows significant reduction of short-channel effects. The threshold voltage role-off decreases as the fin height decreases. In nano scale FinFET have short channel effects are eliminated significantly when the fin width is less than the fin height [8].

Doped FinFETs retain a variability advantage over conventional planar technology, if the channel doping is lower than a few  $10^{18}/\text{cm}^3$ [9].

The new Body-on-insulator FinFET can suppress the source/drain leakage beneath the channel region; it can maintain low S/D parasitic resistance and good heat dissipation capability, this device shows an effective suppression of the leakage current and excellent immunity to short-channel effects [12]. M.Nawaz et al. [35] have shown that the bulk FinFETs were approximately independent of back bias effect, with identical fin geometry bulk FinFETs and anti-punch implant shown the same Ion-Ioff behavior and approximately equal short channel effect like SOI (Silicon On Insulator) FinFETs.

# **1.2 IMPROVEMENTS IN POWER AND AREA MINIMIZATION**

FinFET logic circuits achieve significant area and power reduction without voltage or transistor scaling even though they suffer greatly in circuit speed [14]. FinFET based processors allows lead to large spreads in delay & leakage under PVT(Process, Supply Voltage, Temperature)variations [15].Multi threshold voltage FinFET sequential circuit effective in reducing the power consumption under process parameter variations [16].

Feng Wang et al. [17] and it has been shown that FinFET circuits have better soft error immunity, and it has less vulnerable to process variation, FinFET-based circuit designs are much robust than the bulk CMOS counterparts.

Michael A.Turi et al. [26] have proposed a promising scheme of SG-high precharge swing scheme, it had some of the features delay was 48.1% and 59.9 % (less than the minimum low power scheme). Temperature has an exponential effect on leakage current and small effect on dynamic current.

#### 2. ARCHITECTURE MODIFICATION FOR IMPROVING PERFORMANCES

Ting-Jung Lin et al. [19] have designed a Fine-grain Dynamically Reconfigurable 2.0 architecture (FDR) in that the logical elements is augmented with dedicated carry logic to facilitate arithmetic operations, The experimental result shown that the coarse-grain design can improve performance by 3.6Xcompared with the fine-grain FDR architecture, they have designed 22-nm FinFET technology, it enables more flexible and effective power management. Francesco Conzatti et al. [21] described the strain engineering in n and p type FinFETs by using strain measurements, mobility characterization and physical-based modeling. they have analyzed that the electron and hole measured mobility was found to be fairly insensitive to the fin width, then the simulation result shown that the electron mobility can be further improved by tensile strain in fin length direction, whereas the hole mobility can be increased by using a compressive strain in the same direction.

Vladimir Jovanovic et al. [23] have demonstrated the technology for ultra-high aspect ratio FinFETs on bulk silicon wafers. They have analyzed on nano scale gate length of FinFET fabrication process and reduction of source/drain series resistance would result in accessible technology well suited for high-frequency analog applications. Debajit Bhattacharya et al. [18] have presented a paper of Layout-based parasitic-aware design space exploration of FinFET content addressable memory, and also they observed that leakage power assumes slightly greater significance with a decreasing mismatch probability. Finally they observed noticeable differences in parasitic capacitance between two orthogonal layout styles (VSL &VML).

T.Rudenko et al. [24] shown that the narrow FinFET structure has reduced gate current densities compared to the quasi-planar (very wide fin) structures. This reduction was observed in both doped & undoped channel devices. M.Poljak et al. [25] have proposed a solution for the suppression of corner effects and related kink effect in wide-channel triple gate bulk FinFETs. In this method it does not require no additional masks, also they have obtained threshold voltage shift were 0.434V &0.287V. Field Enhancement of FinFET allows high program and erase speed and larger memory window, this programming and erasing characteristics must be taken into account in memory circuit design [13].

#### **2.1 IMPROVEMENTS IN NOISE REDUCTION**

Tatsuya OHGuro et al. [28] have proposed technique on fin patterning due to Side-Wall Transfer (SWT). This technique is useful to not only fabricate narrow fin line but also suppress fin width variation. The  $H_2$  annealing after Si etching is useful for not only to improve the mobility of electron and hole but also to reduce flicker noise of FinFET. The noise in FinFET with fully depletion mode decreases which are similar to ultra thin SOI device, however FinFET has the disadvantage for RF performance due to larger gate capacitance comparing with planar MOSFET. Yiming Li and Chih-Hong Hwang [29] have analyzed 16nm bulk FinFET on the characteristics of random dopant effects. The result shown that for the same threshold voltage the immunity against fluctuation of the 16nm FinFET is superior to the planar device. It is about 2.5 times reduction. E.Simoen et al. [30] have proposed paper on multiple-gate MOSFETs seem to yield acceptable 1/f noise levels and appear to be quite robust against floating body effect, for ultra-thin film devices, the quantization effects will become more & more important, this may also reflect in the low frequency noise behavior.

V.Subramanian et al. [31] have examined the impact geometrical parameter of fin width of FinFET devices, for fin width in the range of 25-75nm, the front gate coupling coefficient was small ( $\sim$ 0.01), the trans conductance tocurrent ratio is weakly sensitive to fin widths, low frequency noise increases for narrow fins, which points to increased (1.5 times) interface trap density of fin side walls compared to the top surface.

# 2.2 IMPROVEMENTS OF SCALABILITY USING MULTIGATE FINFET TECHNIQUES

Romain Ritzenthaler et al. [5] have presented paper on pigate FETs, they described that increasing the number of gates allows a better scalability of multiple gate FET SOI devices, pi-gate FETS acting like a device with a number of gates between 3 & 4 offers increased front-gate control.

Mirko Poljak et al. [32] have shown that bulk FinFET with Source/Drain-to-body(S/D) junction shallower than gatebottom has equal or better sub threshold performance than SOI FinFET. By reducing S/D junction depth, fin-width scaling for suppression of short-channel effects can be relaxed and bulk FinFET characteristics can be improved with no increase on process complexity &cost.

M.A. Pavanello et al. [33]analyzed the analog performances of nMOS triple-gate FinFETs with undoped body and TiN/HfO2/Sio2 gate stack using narrower FinFETs increases the early voltage with respect to wider ones when the device are operating in the onset of volume inversion. The mobility of long channel narrow FinFETs was observed to be larger than for wider ones improving the transconductance over drain current ratio in moderate inversion regime. The omission of the halo implantation improves both the carrier mobility & the early voltage for devices longer than 100nm, for FinFETs with un doped body and no halo implantation large gain devices can be achieved n-type FinFET have the potential improvements on current drive and trans conductance –to-drain current ratio than bulk.

# 2.3 MODELING OF ASYMMETRIC GATE WORK FUNCTION

Ajay N.Bhoj et al. [34] have evaluated Symmetric-Gate work function SG/IG-mode FinFET and Asymmetric-gate work function SG-mode FinFET head to head in a highperformance process and the result shown that Asymmetric gate work function SG-mode FinFETs with high-performance provide very steep sub threshold slopes. Ultra-low off

currents and high-on currents in comparison to symmetric gate work function SG/IG-mode FinFETs. Single IG-mode device is sufficient to reduce leakage considerably without too much degradation in delay. Ajay N.Bhoj et al. [27] have shown that Asymmetric gate work function FinFET SRAM bit cells had a better dynamic write ability, Symmetric gate work function had unattractive transient characteristics. K.Bennamance et al. [36] have found that the low field mobility was significantly degraded at small gate length in sub 100nm FinFETs and also demonstrated that the side wall mobility was about 25-30% lower as compared to the top surface conduction, the trap density in high conductivity metal gate stack has been found much larger than in pure Sio2 MOSFETS but with no further degradation at small fin widths with low frequency noise previous findings on fully depleted-SOI devices. T.Chiarella et al. [37] have developed on DOI substrates and low doped fins results in lower junction capacitance, higher mobility and voltage gain with reduced threshold voltage mismatch using an optimized integration to minimize parasitic capacitances and resistance and also they have demonstrated high-performing FinFET ring-oscillators with delays down to 10ps/stage for both SOI &bulk FinFETs.

Jaw-Juinn Horng et al. [38] have presented paper on combination structure of temperature & voltage sensor in a 16nm FinFET technology. The temperature sensor achieved 1°C resolution over -10 ~90°C range, the voltage sensor achieved 4mv output error over 0.38v to 0.56v. The total chip size is  $0.01 \text{mm}^2$  and drawn 70uW total power from a 0.7V supply, depending on resolution the measurement time can change from 10µsec to 1.6ms.

# 2.4 SRAM based FinFETs performances

Double gate-FinFET based static random access memory reduces the soft error failure rate [7]. Lightly doped silicon fin improves the immunity to random do pant fluctuation, making a FinFET a promising candidate for subthreshold SRAM applications [10]. Ming-Long Fan et al. [11] have presented paper on FinFET and they found that 4T FinFET SRAM cell exhibits a better nominal Read static Noise margin than the conventional 6T cell. Kyoman Kang et al. [20] have proposed a differential SRAM architecture with a full swing local bit line. This architecture stores four bits in one block can achieve a minimum voltage of 0.42V and Read delay is 62.6 times lesser than that of 8T SRAM based 22nm FinFET technology. Mayank Shrivastava et al. [22] have presented paper on Implant-Free (IF) complementary metal-oxide semiconductor that gave better scalability with improved performance. The result has shown that approximately two times improvement in static random access memory and digital input/output performance.

International Research Journal of Engineering and Technology (IRJET)e-ISSN: 2395-0056Volume: 04 Issue: 07 | July -2017www.irjet.netp-ISSN: 2395-0072

### **3. CONCLUSIONS**

From the results, derived in research papers, it is concluded that FinFETs are extremely fast and power efficient devices, its disadvantage being difficulties in fabricating it to perfection, being a very small device and its series resistance and extrinsic parasitic capacitance. Few papers have suggested changes in geometries, dimensions, change in materials used etc. They yielded considerable advancements in drain current, speed, threshold voltage, etc. Out of all, inclusion and change in spacers used proved a considerable improvement over others. They play a major role in deciding the parasitic capacitance of the FinFET. As there is a reduction in capacitance, they offer great performance in analog applications, in which these devices lag also, the threshold voltage is reduced because of which, power consumption too reduced. This can pose great advantage in using FinFETs for analog and high speed devices. The disadvantages of noise and low speed restricted from use of FinFET in such devices.

#### REFERENCES

[1] T.-J. King, "FinFETs for nanoscale CMOS digital integrated circuits," in Proc. Int. Conf.Computer-Aided Design, Nov. 2005, pp. 207–210

[2]E.J.Nowak,I.Aller,T.ludwig,K.Keun woo,R.V.Joshi, et al, "Turning silicon on its edge[double gate CMOS/FinFET technology],"IEEE circuits devices mag. Vol 20, no.1. pp.20-31. Jan 2004.

[3] Zia Abbas,Antonio Mastrandrea &Mauro olivieri, " A Voltage –Based leakage current calculation scheme and its application to Nanoscale MOSFET & FINFET Standard-cell design",IEEE transcations on Very Large scale Integration (VLSI) Systems,vol.22,no.12,December 2014.

[4] Yang Yang &Niraj K.Jha, "FinPrin:FinFET logic circuit analysis and optimization under PVT Variations,"IEEE trans. On Very Large Scale integration (VLSI) Systems, vol.22,no.12,Dec.2014.

[5]Romain Ritzenthales,Oliver Faynot,sorin Cristoloveanu,Benjamin Iniguez, "3D analytical modeling of subthreshold characteristics in vertical multiple-gate FinFET transistor," Solid-state Electronics 65-66(2011) 94-102.

[6] Rajesh A. Thakker, Mayank Srivastava, Ketan kumar et al, " A Novel architecture for improving slew rate in FinFETbased op-amps and OTAs" microelectronics journal 42(2011) 758-765.

[7]S.S.Rathod,A.K.Saxena,S.Dasgupta, "A proposed DG-FinFET based SRAM cell design with rad Hard capabilities", microelectronics reliability 50(2010) 1181-1188.

[8] Fasarakis, A. Tsormpatzoglou, D.H. Tasis, C.A. Dimitriadis, K.R apatharqsiou. J. Jovach, "Analytical unified threshold voltage

model of short-channel FinFET & implementation", solidstate electronics 64 (2011) 34-41.

[9]C.H.Lin,R.Kambhampatti,R.J.Miller,T.B.Hook et al, "channel doping impact on FinFET for 22nm and beyond" symposium on VLSI technology digest of technical papers -2012.

[10]M.L.Fan, Y.S.Wu,V.P.H,Hu,P.Su and C.T chuang, "Investigation of cell stability and write ability of FinFET subthreshold SRAM using analytical SNM model," IEEE Transaction Electron Devices, vol. 57, no.6. pp (1375-1381) June 2010.

[11] Ming-Long Fan,Yu,Shengwu.vita pi-HoHu, Chien-Yu Hsieh, Pin su & Ching –Te Chuang, "comparison of 4T and 6T FinFET SRAM cells for subthreshold operation considering variability- A model-based approach", IEEE trans. on Electron Devices, vol.58,no.3. March 2011.

[12] Xiaoyan xu,Runsheng wang,Ru Huang, Jing zhuge,Gang chen,xing zhang,Yangyuan wang," High-performance BOI FinFETs based on bulk-silicon substrate," IEEE trans on Electron Devices, vol.55,no.11. Nov.2008.

[13] Tzu-Hsuan Hsu,Hang-Ting lwe,Ya-chin kim,Yi-Hsuan Hsiao,et al, "physical model of Field Enhancement and edge effects of FinFET charge trapping NAND Flash devices," IEEE trans. On Electron Devices, vol.56,no.6. June 2009.

[14] Michael C.Wang, "Independent –Gate FinFET circuit design methodology", IAENG International Journal of Computer Science,IJCS-37-1-06.

[15] Aoxiang tang, yang Yang, Chun-Y,lee,Niraj K.Jha, "μCpatpvt: Delay and power modeling framework for FinFET processor Architectures under PVT Variations",IEEE trans. On Very Large Scale Integration (VLSI) System-2014.

[16] Sherif A.Tawtik and Volkan kursun, "Multi-threshold voltage FinFET Sequential circuits," IEEE trans. On Very Large Scale Integration(VLSI) System vol.19.no.1.Jan 2011.

[17] Feng wang,Yuan Xie,Kerry Beinstein,Yan luo, " Dependability Analysis of Nano-scale FinFET circuits," IEEE emerging VLSI technologies and Architectures, 2006.

[18] Debajit Bhattacharya, Ajay N.Bhoj and Niraj K.Jha , " design of efficient Content Addressable Memories in Highperformances FinFET Technology," IEEE trans. On Very Large Scale Integration (VLSI) System vol.23, no.5,May 2015.

[19] Ting. Jung Lin, Wei Zhang, Niraj K.Jha, "FDR 2.0: A Lowpower Dyanamically reconfigurable Architecture and its FinFET implementation," IEEE trans. On Very Large Scale Integration(VLSI) System, sep ,2014.

[20] Kyoman Kang,Hanwool Jeong,Youngwi,Yang,Juhyuan Park,Kiryoung kim,Seong-ook Jung, "Full-swing local Bitline SRAM Architecture Based on the 22-nm FinFET technology for low-voltage operation,' IEEE trans. On Very Large Scale Integration (VLSI) System, June 9.2015.

[21] Francesco conzatti,Nicola Sera,David Esseni, Marco De ,Alan Paussa et al, " investigation of strain engineering Analysis and Numerical Simulations," IEEE trans. On Electron Devices, vol.58, no.6, June 2011.

[22] Mayank Shrivastava, Ruchit Mehta, Shashank Gupta, Nidhi Agarwal, maryan shojali Baghini, et al, "Toward system on chip (soc) Development using FinFET Technology: challenges, solutions, process co-development & optimization Guidelines," IEEE trans. On Electron Devices, vol.58, no.6, June 2011.

[23] Vladimir Jovanovic, Tomislav Suligoj, Mirko poljak, Yann civale, Lis K.Namver, "Ultra-high aspect-ratio FinFET technology,"solid-state electronics, 54(2010) 870-876.

[24]T.Rudenko,V.Kilchytsta,N.Collaert,M.Jurezak, "Reduction of gate-to-channel tunneling current in FinFET structures," solid-state electronics 51(2007) 1466-1472.

[25] Mirko Poljak,Vladimir Jovanovic,Tomislav suligoj, " Suppression of corner effects in wide-channel triple-gate bulk finFETs," microelectronic engineering 87 (2010) 192-199.

[26]Michael A.Turi,Jose G.delgado-Frias,Niraj K.Jha, "Lowpower finFET design schemes for NOR Address Decoders," IEEE. 2010.

[27] Ajay N.Bhoj,Niraj K.Jha, " Parasitics Aware design of symmetric and Assymmetric Gate-work function FinFET SRAM,"IEEE trans. On (VLSI) System,vol.22,no.3, March 2014.

[28]Tatsuya OHGURO, Satoshi INABA,Akio KANEKO,Kimitoshi OKANO,"Technology of FinFET for high RF and Analog/Mixed-signal performance circuits, " IEICE trans. Electron.,vol.E98-c,no.6.June 2015.

[29] Yiming Li and Chih-Hong Hwang, "Electrical Characteristics Fluctuation in 16nm bulk-FinFET devices," microelectronic engineering 84 (2007)2093-2096.

[30]E.simoen,A.Mercha,C.Clarys,N.Lukyanchikova,"Low-frequency noise in silicon-on-insulator devices and technologies," solid-state electronics 51(2007) 16-37.

[31]V.Subramanian,A.Mereha,B.Parvais,J.Loo,et al, "Impact of fin width on digital and anlog performances of n-FinFETs," solid-state electronics 51(2007)551-559.

[32]Mirko Poljak, Vladimir Jovanovic,Tomislav suligoj, " Improving bulk FinFET DC performance in comparison to SOI FinFET," microelectronic engineering 86(2009) 2078-2085.

[33]M.A.Pavanello,J.A.Martino,E.Simoen,R.Rooyackers,N.Coll aert,C.Clarys, "Kvaluation of triple-gate FinFETs with Sio<sub>2</sub>- $_{Hfo2}$ -TiN gate stack under analog operation," solid-state Electronics 51 (2007) 285-291.

[34] Ajay N.Bhoj,Niraj K.Jha, "Design of logic gates and flipflops in High-performance FinFET Technology, IEEE trans.OnVeryLargeScaleIntegration(VLSI)

System, vol.21.no.11.Nov.2013.

[35] Muhammad Nawaz,Stefan Deckar et al, "Evaluation of process parameter space of bulk FinFETs using 3D TCAD," microelectronic engineering 85(2008)1529-1539.

[36]K.Bennamance,T.Boutchacha,G.Ghibaudo,M.Mouis,N.Coll art, " DC and lowfrequency noise characterization of FinFET devices," solid-state electronics 53(2009) 1263-1267.

[37]T.Chiarella,L.Witters,A.Mercha,C.Kerner,M.Rakowski, et al, "Benchmarking SOI and bulk FinFET alternatives for planar CMOS scaling succession" solid-state electronics 54(2010) 855-860

[38] Jaw-Juinn Horng,Szu-Lin Liu,Amit Kundu,Chin-Ho chang,Chung-Hui chen,Herman Chiang,Yung-chow peng, "A 0.7 V resistive sensor with temperature/voltage detection function in 16nm FiNFET technologies" IEEE sumposium on VLSI Circuits Digest Of Technical papers,2014.

ISO 9001:2008 Certified Journal

Т