# A study of CMOS inverter using 65nm technology

## Manjeet kumar

Student, Electronics and communication engineering department, NIT SIKKIM, SIKKIM, INDIA

**Abstract** - The inverter is the backbone of any digital circuit which can perform Boolean operation on the single input variable. At present world low power device design and its implementation have got a significant role in the field of nano-electronic circuits. In this paper we have optimized the CMOS inverter design in 65nm technology and verified its operation using cadence virtuoso tool.

Key Words: CMOS, p-MOS, n-MOS, threshold voltage  $V_{\rm t}$  , Noise margin ,PDP.

## **1. INTRODUCTION**

The inverter is the most fundamental logic gate that can perform a Boolean operation on a single input variable. The CMOS inverter consists of an n-mos and a p-mos transistor operating in complementary manner. It behaves like a complementary push pull in the sense for the high input (on state), the p-mos transistor is off and the n-mos transistor act as a load and for the low input (off state) the p-mos transistor drives (pulls up) the output load while the n-mos transistor is off. The CMOS inverter has two major advantages. First the steady state power dissipation of CMOS inverter circuit is negligible (except for a small leakage current) so it offers low power dissipation and second the voltage transfer characteristic (VTC) exhibit a full output voltage swing between 0V and  $V_{DD}$  i.e. will operate over a wide range of source and input voltages (provided the source voltage is fixed).Besides this it shows a high noise margin and has relatively high speed of operation [1].It is also known for the amplification of analog signal when it is operated at the middle of the VTC ,when both the transistor is in the saturation mode.

## **1.1 CMOS inverter structure**

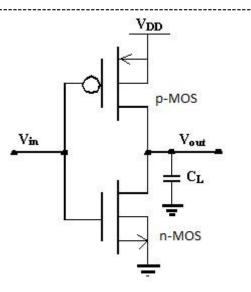

The CMOS inverter is realized by the series connection of a p-MOS and n-MOS. Both their gates are connected to the input line and their drains are connected to the output. For avoiding the short channel effect the body of both the MOS is connected to their respective sources.

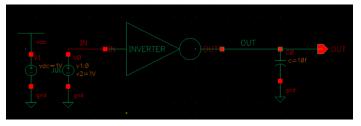

Fig 1: Structure of CMOS inverter

## **1.2 CMOS inverter operation**

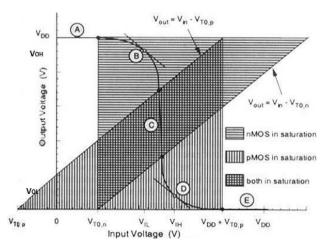

The operation of the circuit can be explained with the help of diagram followed by the table:

Table -1: Operation of the CMOS inverter

| Reg | Vin                 | Vout             | n-mos      | p-mos  | Comm                  |

|-----|---------------------|------------------|------------|--------|-----------------------|

| ion |                     |                  |            |        | ents                  |

|     | < V <sub>To,n</sub> | V <sub>OH</sub>  | Cut-off    | Linear | Output~V <sub>D</sub> |

| А   |                     |                  |            |        | D                     |

|     | VIL                 | High             | Saturation | Linear | Slope=-1              |

| В   |                     | ~V <sub>OH</sub> |            |        | -                     |

International Research Journal of Engineering and Technology (IRJET) e-

JET Volume: 04 Issue: 10 | Oct -2017

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

| ſ |   | $V_{th}$             | $V_{th}$      | Saturation | Satura  | VIN =   |

|---|---|----------------------|---------------|------------|---------|---------|

|   | С |                      |               |            | tion    | VOUT    |

| ſ |   | V <sub>IH</sub>      | Low           | Linear     | Satura  | Slope = |

|   | D |                      | $\sim V_{OL}$ |            | tion    | -1      |

|   |   | >(Vdd                | Vol           | Linear     | Cut-off | Output~ |

|   | Е | +V <sub>To,p</sub> ) |               |            |         | 0V      |

## 1.3 Noise Margin

It is the amount of noise that a CMOS circuit could withstand without compromising the operation of circuit.

Low Noise margin  $N_{ML}=V_{IL}-V_{OL}$ High noise margin  $N_{MH}=V_{OH}-V_{IL}$ For an ideal CMOS Inverter Noise margin  $NM=N_{ML}=N_{MH}=V_{DD}/2$

## **1.4 Power dissipation**

The static power dissipation of the CMOS inverter is very negligible as it does not draw any significant current from the power source in both the steady state operating points. There is a small current which is actually a reverse leakage current due to short channel effect. It is given by  $I_{sat} * V_{DD}$

The dynamic power dissipation occurs during switching from high to low and vice versa and during this period CMOS inverter conducts a significant amount of current. Dynamic power (PD) =  $C_L * V_{DD} * frequency$

So power is a function of load capacitance ( $C_L$ ), power supply and frequency of operation. A reduction of any one factor will reduce the power consumption and thus reduce the heat developed in the device.

The total power dissipation is the sum of both the powers which is very less with major contribution of dynamic power. This makes CMOS technology attractive in low power and high-density applications.

## 2. Simulated Result

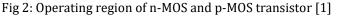

The conventional CMOS is designed using TSMC 65nm PDK in cadence virtuoso tool with  $W_P/W_N$  ratio of ~2.3, operating at 1V  $V_{\text{DD}}$  supply.

Fig:3 Schematic diagram of CMOS inverter

We assume that all parasitic capacitances are lumped together into one single capacitor  $C_L$  [2]. The CMOS inverter is operated with a square pulse input waveform.

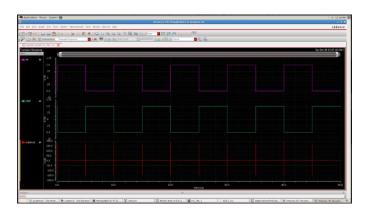

Fig 4: Transient analysis of CMOS inverter with  $C_{\rm L}$  as as load

Fig 5: Transient behavior of CMOS inverter (i) VIN (ii) VOUT (iii)  $I_{\text{C}}$

The capacitance current Ic is almost negligible in the static region and is significant during transitions. This dynamic current occurs as a result of the p-MOS and n-MOS simultaneously transitioning through their linear region. These two continuous current peaks during transition in opposite direction aren't equal; since the total current being drawn through the p-MOS is being split between the output path and the n-MOS path.

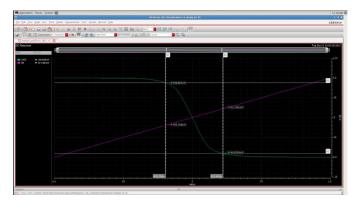

Fig 6 : VTC of the CMOS inverter.

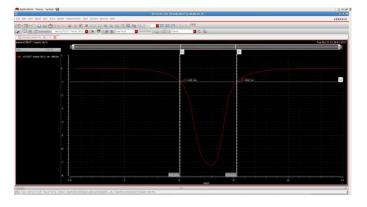

Fig 7: VTC derivative curve of CMOS inverter.

The highlighted derivative value represents the points where the slope of VTC is exactly -1 i.e. points of  $V_{IL}$  and  $V_{IH}$ .

## **3. CONCLUSIONS**

In this paper an optimized COMS inverter is designed with 65 nm technology .The dc and the transient analysis of the purposed designed is verified using Cadence virtuoso tool. The power dissipation shown by the CMOS inverter is only a few nW ( $\sim$ 1.5) so it gives a less heat stress and thus a good reliability. Less power consumption also extend the battery life in battery powered system. The CMOS inverter is used in analog circuits, digital circuits, ring oscillator etc. Some interesting issue like PDP, rise and fall time etc remains to be investigated.

## ACKNOWLEDGEMENT

I would like to thank my faculty members and my friends for their sincere guidance and motivation.

## REFERENCES

- [1] S. M. Kang and Y Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design," 3rd edition, McGraw Hill, 2004.

- [2] Jan.M Rabay,Digital Integrated Circuits: A Design Perspective, Prentice Hall India Learning Private Limited; 2 edition ,2003.

- [3] K. D. Buddharaju, N. Singh, S. C. Rustagi, Selin H. G. Teo, L. Y. Wong, L. J. Tang, C. H. Tung, G. Q. Lo,N. Balasubramanian, and D. L. Kwong, "Gate-All-Around Si-Nanowire CMOS Inverter Logic Fabricated using Top-down Approach", IEEE, 2007, pp: 303-306

- [4] Xiaoxia Wu Feng Wang Yuan Xie, "Analysis of sub threshold Finfet circuits for ultra-low power design" International Journal of Scientific & Engineering Research, Volume 2, Issue 2, April 2011.

- [5] Tzu-Chi Wang; Jyi-Tsong Lin; Kai-Cheng Juang; Wei-Han Lee; Ting-Pi Hsu; Jing-Hao Lai "A novel low bias and high speed non-classical CMOS inverter with unique shared contact" IEEE 2016