## International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395 -0056

Volume: 04 Issue: 01 | Jan -2017 www.irjet.net

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

## A Novel Transformer-less Four Phase Buck Converter with Low Voltage Stress and Automatic Current Sharing

#### Fousia Sainudheen

PG Scholar, Department of Electrical and Electronics Engineering, Ilahia College of Engineering and Technology, Mulavoor P O, Muvattupuzha, Kerala, India

**Abstract** - An Interleaved high step-down conversion ratio buck converter with closed loop control for low switch voltage stress. In this converter two input capacitors are seriescharged by the input voltage and parallel discharged by a new four - phase IBC (Interleaved Buck Converter) for providing a much higher step-down conversion ratio without adopting an extreme short duty cycle. Based on the capacitive voltage division, the main objectives of the new voltage-divider circuit in the converter are both storing energy in the blocking capacitors for increasing the step-down conversion ratio and reducing voltage stresses of active switches. As a result, the converter possesses the low switch voltage stress characteristic. Moreover, due to the charge balance of the blocking capacitor, the converter features automatic uniform current sharing characteristic of the interleaved phases without adding extra circuitry or complex control methods. Closed loop simulation using PI controller of the new IBC converter is done with 400 V DC input and 500 W output power.

*Key Words*: Interleaved, Four Phase, Automatic current sharing, Voltage stress, IBC...

#### 1.INTRODUCTION

Nowadays high performance dc – dc converters are required for increasing high step-down conversion ratio with high output current applications like CPU boards and battery chargers, and distributed power systems [2] – [4]. For non-isolation applications with low output current ripple requirement, an interleaved buck converter (IBC) has received a lot of attention due to its simple structure and low control complexity.

Interleaving technique connects dc-dc converters in parallel to share the power flow between two or more conversion chains it implies a reduction in the size, weight and volume of inductors and capacitors. Also a proper control of the parallel converters increase the ripple frequency and reduces the ripple waveforms at the input and output of the power conversion system, which leads significant reduction of current, voltage ripples and filter capacitor size. Therefore the interleaved buck converters has received a lot of attention in non-isolation applications with low output current ripples.

However, in the conventional multiphase IBC, as shown in active switches are required to use high-voltage devices that are rated above the input voltage. High-voltage-

rated devices generally render a number of undesirable characteristics, such as high cost, large on-resistance, large voltage drop, and severe reverse recovery. For high-input low-output voltage regulation applications, operations at higher switching frequencies are required to achieve a higher power density and better dynamics [5]. However, the buck converter with a high step down conversion rate yields a significant switching loss due to its extremely low duty cycle. This fact not only limits the achievable switching frequency, but also complicates its implementation. In addition, the efficiency is further compromised due to the short on-time and long freewheeling time within each switching cycle [6].

To overcome such disadvantages of the conventional IBC, a number of modified IBC structures have been proposed [7]–[14]. A multiphase IBC with extended duty ratio [7], [8] was proposed for high-input low-output voltage regulation applications. Two and four-phase versions of the topology were examined in [7] and [8]. The four-phase extended duty ratio IBC The mechanism of the extended duty ratio lies in the use of highly efficient input voltage dividers which reduce the switching voltage and the associated losses. However, the voltage stress to input switching devices remains rather high.

In this paper, we propose a novel transformer-less dc converter that features low switch voltage stress and automatic uniform current sharing. An interleaved fourphase voltage divider is used to achieve a high step-down conversion ratio. In the proposed converter, series charging of the two capacitors from the input voltage and parallel discharging to the load facilitated by a new four phase IBC. This architecture provides a high step-down conversion ratio and a low output current ripple without requiring an extremely low duty cycle. Based on the capacitive voltage division, the new voltage-divider circuit in the converter achieves two major objectives, i.e., increased voltage conversion ratio, due to energy storage in the blocking capacitors, and reduced voltage stress of active switches. The low switch voltage stress offered by the proposed converter topology allows the use of lower voltage rating MOSFETs to reduce both switching and conduction losses, thereby improving the overall efficiency. Moreover, due to the charge balance of the capacitors, the converter features automatic uniform current sharing of the interleaved phases without adding extra circuitry or complex control methods.

www.irjet.net

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

# 2. NOVEL TRANSFORMER-LESS FOUR PHASE BUCK CONVERTER

Volume: 04 Issue: 01 | Jan -2017

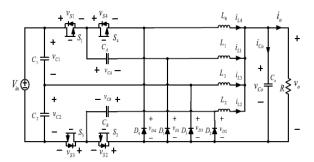

The proposed converter is shown in Fig. 1, which is derived from the two-phase IBC with an extended duty ratio in [9]. In order to further reduce the output current and output voltage ripples, the converter is divided into fourphase small inductors via an interleaved operation. It is clear from Fig. 1 that the proposed converter consists of four inductors, four active power switches, four diodes, and four capacitors. The proposed converter topology with low switch voltage stress and high step down ratio can only be achieved when the duty cycle is lower than 0.5 and operated in CCM. In addition, when the duty cycle is lower than 0.5, due to the charge balance of the blocking capacitor, the converter enables automatic current sharing so as to obviate any extra current-sharing control circuit. On the other hand, when the duty cycle is higher than 0.5 or when the converter is operates under DCM with a light load, the converter no longer possess the automatic current-sharing capability, and the current-sharing control between each phase should be taken into account.

Fig 1. Circuit Diagram of Proposed IBC

#### 3.MODES OF OPERATION

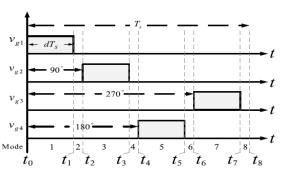

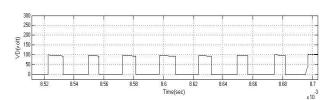

In order to clearly explain the operation principle, the operating duty ratios 0 < D < 0.25 and 0.25 < D < 0.5 by the proposed four-phase and two-phase interleaved strategies are, respectively, introduced. Referring to the gate signals shown in Fig. 2, the corresponding operating modes of the proposed converter for condition 0 < D < 0.25 is discussed next. In first mode, switch S1 is turned on, and switches S2, S3, and S4 are all OFF. Hence, diode D1 becomes OFF whereas diodes D2, D3, and D4 remain ON. The stored energy of C1 is discharged to CA, L1, and the output load, whereas current iL2, iL3, and iL4 are freewheeling through D2, D3, and D4, respectively. In the next mode all switches gets off. In this case, iL1, iL2, iL3, and iL4 are freewheeling through diodes D1, D2, D3, and D4, respectively. In next mode only S2 gets on an all others off. Corresponding changes as in mode 1 continues.

Fig 2. Gate Pulse of four phase strategy

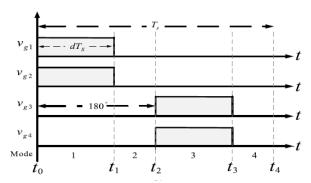

Referring to the gate signals shown in Fig. 3, In first mode two switches S1 and S2 gets on It is observed that iL3 and iL4 are freewheeling through D3 and D4, respectively, and L3 and L4 are releasing energy to the output load. The stored energy of C1 is discharged to CA, L1, and the output load, while the stored energy of CB is discharged to L2 and the output load. In the next mode all switches are off. In this case, iL1, iL2, iL3, and iL4 are freewheeling through diodes D1, D2, D3, and D4, respectively. During next mode other pair of switches gets on and current flow continues.

Fig 3. Gate Pulse of two phase strategy

#### 4.DESIGN

From the volt-second relationship on

inductors  $L_1 - L_4$ , it is obtained as

$$(V_{C1} - V_{CA} - V_0)D - V_0(1 - D) = 0$$

$$(V_{CB} - V_0)D - V_0(1 - D) = 0$$

$$(V_{C2} - V_{CB} - V_0)D - (1 - D)V_0 = 0$$

$$(V_{CA} - V_0)D - (1 - D)V_0 = 0$$

From the above equation, it can be

derived as

$$MStep-down = \frac{Vo}{Vin} = \frac{D}{4}$$

The components are designed based on the assumption that all components are ideal, the capacitors are large enough that the voltage across them can be considered

as constant also C1=C2 and CA = CB.

$$V_{O} = \frac{D}{4} \times V_{I}$$

$$L_{1} = L_{2} = L_{3} = L_{4} = \frac{V_{O}T_{S}(1-D)}{\Delta IL}$$

$$C_{A} = C_{B} = C_{1} = C_{2} = \frac{\Delta ILDT_{S}}{2\Delta V_{C}}$$

$$C_{O} = \frac{\Delta IL}{8(\Delta V_{O} - \Delta IL *ESR)f_{S}}$$

Volume: 04 Issue: 01 | Jan -2017

#### **5.SIMULATION RESULTS**

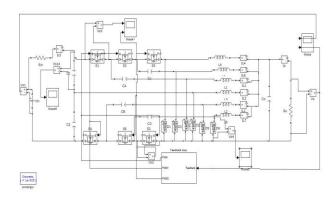

The closed loop Simulation of the above converter is done in MATLAB simulink using 400 V input and 24 V, 500 W output at 40 KHZ frequency. The Parameters used in Simulation are shown in Table 1

Table 1. Parameters Used in Simulation

| Sl | Parameters Used            | Specification |

|----|----------------------------|---------------|

| No | Turumovers obea            | opeomeanism   |

| 1  | Inductors                  | 250μΗ         |

| 2  | Capacitors C <sub>A,</sub> | 10 μF         |

|    | $C_{B_1}C_{1_1}C_2$        |               |

| 3  | Output Capacitor           | 220 μF        |

|    | Со                         |               |

| 4  | Output Resistor            | $1.152\Omega$ |

|    |                            |               |

| 5  | Duty Ratio                 | 24            |

| 6  | Output Power               | 500 W         |

| 7  | Frequency                  | 40KHz         |

| 8  | Input Voltage              | 400V          |

| 9  | Output Voltage             | 24 V          |

Fig 4 Closed Loop Simulation Diagram

The output Waveforms of the Proposed converter is shown below

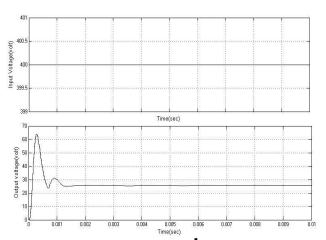

Fig 5 Input and Output Voltages

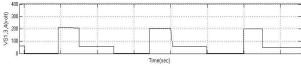

Fig 6 Voltages stresses across switches

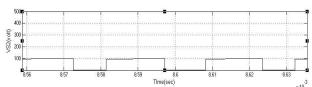

Fig 7 Voltages stresses across Diodes

After simulation the output voltage obtained is shown Fig 5. the circuit was designed for a 24v output, which was obtained after simulation. The Voltage stresses across the switches and diodes are obtained as already known theoretical results

$$V_{D1}$$

,max =  $V_{D2}$ ,max =  $V_{D3}$ ,max =  $V_{D4}$ ,max =  $\frac{Vin}{4}$  = 100 V

$$V_{S1,max} = V_{S3,max} = V_{S4,max} = \frac{Vin}{2} = 200 \text{ V},$$

$$V_{S2}, \max = \frac{Vin}{4} = 100 \text{ V}$$

#### 6. CONCLUSIONS

In this paper, an interleaved high step-down conversion ratio dc–dc converter with low switch voltage stress has been proposed. In the proposed converter, two

### International Research Journal of Engineering and Technology (IRJET)

Volume: 04 Issue: 01 | Jan -2017 www.irjet.net p-ISSN: 2395-0072

input capacitors are series-charged by the input voltage and parallel discharged by a new four-phase IBC for providing a much higher step-down conversion ratio without adopting an extreme short duty cycle. Based on the capacitive voltage division, the main objectives of the new voltage divider circuit in the converter are both storing energy in the blocking capacitors for increasing the step-down conversion ratio and reducing voltage stresses of active switches. As a result, the proposed converter topology possesses the low switch voltage stress characteristic. This will allow one to choose lower voltage rating MOSFETs to reduce both switching and conduction losses. Moreover, due to the charge balance of the blocking capacitor, the converter features automatic uniform current sharing characteristic of the interleaved phases without adding extra circuitry or complex control methods. The operation principles and relevant analysis of the proposed converter are presented in this paper

#### **REFERENCES**

- [1]. Chen-Feng Chuang, Member, IEEE, Ching-Tsai Pan, Member, IEEE, and Hao-Chien Cheng" A Novel Transformer less Interleaved Four-Phase Step-Down DC Converter With Low Switch Voltage Stress and Automatic Uniform Current-Sharing Characteristics" IEEE Transactions On Power Electronics, Vol. 31, No. 1, January 2016

- [2]. D. D.-C. Lu and V. G. Agelidis, "Photovoltaic-battery-powered DC bus system for common portable electronic devices," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 849–855, Mar. 2009.

- [3]. K. Sun, L. Zhang, Y. Xing, and J. M. Guerrero, "A distributed control strategy based on DC bus signalling for modular photovoltaic generation systems with battery energy storage," *IEEE Trans. Ind. Electron.*, vol. 26, no. 10, pp. 3032–3045, Oct. 2010

- [4]. M. Pahlevaninezhad, J. Drobnik, P. K. Jain, and A. Bakhshai, "A load adaptive control approach for a zero-voltage-switching DC/DC converter used for electric vehicles," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 920–933, Feb. 2012.

- [5]. X. Du and H. M. Tai, "Double-frequency buck converter," *IEEE Trans. .Ind. Electron.*, vol. 56, no. 54, pp. 1690–1698, May 2009.

- [6]. X. Song, W. Siu-Chung, T. Siew-Chong, and C. K. Tse, "A family of exponential step-down switched-capacitor converters and their applications in two-stage converters," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1870–1880, Apr. 2014.

- [7]. Y. Jang, M. M. Jovanovid, and Y. Panov, "Multiphase buck converters with extended duty cycle," in *Proc. IEEE Appl. Power Electron. Conf.*, Mar. 2006, pp. 38–44.

- [8]. B. Oraw and R. Ayyanar, "Small signal modeling and control design for new extended duty ratio,

interleaved multiphase synchronous buck converter," in *Proc. 28th Annu. Int. Telecommun. Energy Conf.*, Feb. 2006, pp. 1–8.

e-ISSN: 2395 -0056

- [9]. K. Abe, K. Nishijima, K. Harada, T. Nakano, T. Nabeshima, and T. Sato, "A novel multi-phase buck converter for lap-top PC," in *Proc. Power Convers. Conf.*, Nagoya, Japan, Apr. 2007, pp. 885–891.

- [10]. I. O. Lee, S. Y. Cho, and G.W. Moon, "Interleaved buck converter having low switching losses and improved step-down conversion ratio," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3664–3675, Aug. 2012.

- [11]. P. Xu, J. Wei, and F. C. Lee, "Multiphase coupled-buck converter—A novel high efficient 12 V voltage regulator module," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 74–82, Jan. 2003.

- [12]. R. Loera-Palomo, J. A. Morales-Salda na, and E. Palacios-Hern andez, "Quadratic step-down dc-dc converters based on reduced redundant power processing approach," *IET Power Electron.*, vol. 6, pp. 136–145, 2013.

- [13]. J. P. Rodrigues, S. A. Mussa, M. L. Heldwein, and A. J. Perin, "Three level ZVS active clamping PWM for the DC–DC buck converter," *IEEE Trans. Power Electron.*, vol. 24, no. 10, pp. 2249–2258, Oct. 2009.

- [14]. X. Ruan, B. Li, Q. Chen, S. C. Tan, and C. K. Tse, "Fundamental considerations of three-level DC–DC converters: Topologies, analysis, and control," *IEEE Trans. Circuits Syst.*, vol. 55, no. 11, pp. 3733–3743, Dec..