e-ISSN: 2395 -0056 p-ISSN: 2395-0072

# A Seven Level Inverter using a Solar Power Generation System

## Nisha Xavier<sup>1</sup>, Sabeena Salam<sup>2</sup>, Remna Radhakrihnan<sup>3</sup>

<sup>1</sup>Mtech Student, Department of Electrical Engineering, KMEA Engineering College, Edathala, Kerala, INDIA <sup>2</sup>Assistant Professor, Department of Eletrical Engineering, KMEA Engineering College, Edathala, Kerala, INDIA <sup>3</sup>PHD Research Shcolar, Department of Electrical Engineering, CUSAT, Kerala, INDIA

**Abstract** – This paper proposes a new seven level inverter with a solar power generation system, which is composed of a dc-dc power converter and a new seven level inverter. The dcdc power converter integrates a boost converter and a transformer to convert the output voltage of the solar cell array into independent voltage sources with multiple relationships. The most commonly used solar cell model is introduced and the generalized PV model using Mat lab/simulink is developed. Taking the effect of solar intensity and cell temperature, the characteristics of PV model are simulated. This model can be used for analysis of PV characteristics and for simulation with Maximum power point tracking algorithms. This new seven level inverter is configured using a capacitor selection circuit and a full bridge power converter. The capacitor selection circuit converts the two output voltage sources of dc/dc power converter into a three level dc voltage, and the full bridge converter further converts this three level dc voltage into seven level ac voltage. The proposed system generates a sinusoidal output current that is in phase with the utility voltage and is fed into the utility.

Key Words: Maximum power point tracking (MPPT), pulse width modulation technique (PWM), photovoltaic (PV), multilevel inverter.

## 1. INTRODUCTION

The solar energy is becoming more important since it produces less pollution and the cost of fossil fuel energy is rising, while the cost of solar arrays is decreasing. The growing energy demand coupled with the possibility of reduced supply of conventional fuels, along with growing concerns about environmental preservation, has driven research and development of alternative energy sources that are cleaner, renewable and that produce little environmental impact. Among the alternative sources the electrical energy from PV is currently regarded as the natural energy source more useful, since it is free, abundant, and clean, distributed over the earth and participates as a primary factor of all other processes of energy production on earth.

The power conversion interface is more important to grid connected solar power generation systems because it converts the dc power generated by a solar cell array into ac power and feeds this ac power into utility. An inverter is necessary in the power conversion interface to convert the

dc power into ac power. Since the output voltage of solar cell array is low, dc/dc power converter is used in small capacity solar power generation system to boost the output voltage so it can match the dc bus voltage of the inverter. A filter inductor is used to process the switching harmonics of an inverter, so the power loss is proportional to the amount of switching harmonics. The control circuit not only provides PWM signals to switches of two power stages, but also traces maximum PV module energy as well as real time grid detection and protection. The efficiency of conventional boost converter is restricted by duty ratio for higher output voltage. Theoretically, when duty ratio is closed to unity the voltage gain will be infinity.

The conventional multilevel inverter topologies include the diode clamped, the flying capacitor and the cascade Hbridge types. Diode clamped and flying capacitor multilevel inverters use capacitors to develop several voltage levels. But it is difficult to regulate the voltage of these capacitors. In both the diode clamped and flying capacitor topologies 12 power electronic switches are used for seven level inverters. The new seven level grid connected inverter contains only six power electronic switches.

This paper proposes the design and implementation of a PV module inverter. The dc-dc converter with maximum power point tracking control raises the input voltage level into a high voltage level. There is only one MPP (MPP-Maximum Power Point) and this varies according to climatic and irradiation conditions. The photovoltaic power characteristics vary with the level of solar irradiation and temperature which make the extraction of maximum power a complex task. To overcome this problem several methods for extracting maximum power have been proposed. In this paper the maximum power point tracking algorithm uses Perturb and Observe (P & O) method; the method senses the output voltage and current of solar panel to determine the duty cycle of the DC-DC converter to be increased or decreased. The P & O algorithms are widely used in control of MPPT which has simple structure, reduced number of necessary measured parameters and high tracking speed.

The proposed solar power generation system is composed of a dc-dc converter and a seven level inverter. The seven level inverter includes a capacitor selection circuit and a full bridge converter. The seven level inverter contains only six power electronic switches, which simplifies the circuit configuration. Since only one power electronic switch is

ISO 9001:2008 Certified Journal © 2016, IRJET **Impact Factor value: 4.45** Page 421 www.irjet.net

p-ISSN: 2395-0072

e-ISSN: 2395 -0056

switched at high frequency at any time, the switching power loss is reduced and the power efficiency is improved.

Volume: 03 Issue: 09 | Sep-2016

## 1.1 Photovoltaic System

A Photovoltaic (PV) system directly converts sunlight into electricity. The basic device of a PV system is the PV cell. Cells may be grouped into form panels or arrays. The voltage and current available at the terminals of a PV device may directly feed small loads such as lighting systems and DC motors. A Photo voltaic cell is basically a semiconductor diode whose pn junction is exposed to light. Photovoltaic cells are made of of semiconductors using different several types manufacturing processes. The incidence of light on the cell generates charge carriers that originate an electric current if the cell is short circuited.

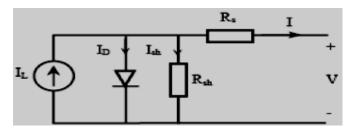

Fig-1: Equivalent circuit of a PV cell

Fig 1 shows the equivalent circuit of a PV cell. In the figure the PV cell is represented by a current source in parallel with a diode. *Rs* and *Rp* represent series and parallel resistance respectively. The output current and voltage from PV cell are represented by V and I.

The I-V characteristics of the solar cell circuit can be sets by the following equations. The current through diode is given by:

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right) \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) / KT \right] \right]$$

$$ID = IO \left[ \exp \left( q \left( V + I RS \right) /$$

While, the solar cell output current:

$$I = IL - ID - Ish (2)$$

I = IL - IO [exp (q (V + I RS)/KT)) - 1] - (V + IRS)/Rsh (3)Where.

I: Solar cell current (A)

IL: Light generated current (A)

IO: Diode saturation current (A)

q: Electron charge (1.6×10-19 C)

K: Boltzman constant (1.38×10-23 J/K)

T: Cell temperature in Kelvin (K)

V: solar cell output voltage (V)

Rs: series resistance  $(\Omega)$ Rsh: shunt resistance ( $\Omega$ )

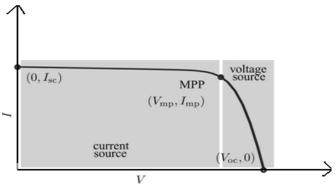

Fig-2: Maximum Power Point (Vmp, Imp)

Characteristic *I–V* curve of a practical PV device and the three remarkable points: short circuit (0, Isc), MPP (Vmp, Imp) and open circuit (Voc, 0).

# 1.2 MPPT Technique

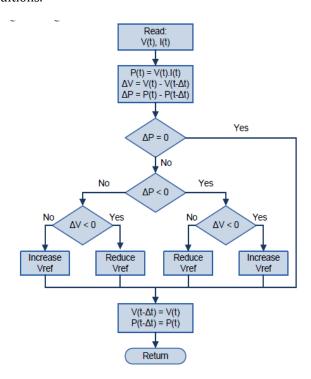

Perturb & Observation algorithms are widely used in MPPT because of their simple structure and the few measured parameters which are required. They operate by periodically perturbing (i.e. incrementing or decrementing) the array termed voltage and comparing the PV output power with that of the previous perturbation cycle. If the power is increasing, the perturbation will continue in the same direction in the next cycle, otherwise the perturbation direction will be reversed. This means the array terminal voltage is perturbed every

MPPT cycle, therefore when the P&O is reached, the P&O algorithm will oscillate around it resulting in a loss of PV power, especially in cases of constant or slowly varying atmospheric conditions. This problem can be solved by improving the logic of the P&O algorithm to compare the parameters of two preceding cycles in order to check when the P&O is reached, and bypass the perturbation stage. Another way to reduce the power loss around the P&O is to decrease the perturbation step, however, the algorithm will be slow in following the P&O when the atmospheric conditions start to vary and more power will be lost.

The P&O method operates periodically incrementing or decrementing the output terminal voltage of the PV and comparing the power obtained in the current cycle with the power of the previous cycle. If the voltage varies and the power increases, the control system changes the operating point in that direction, otherwise change the operating point in the opposite direction. Once the direction for the change of current is known, the current is varied at a constant rate. This rate is a parameter that should be adjusted to allow the balance between faster response with less fluctuation in steady state. The flowchart of this algorithm is presented in Fig.3. A modified version is obtained when the steps are changed according to the distance of the MPP, resulting in higher efficiency. This is an excellent method to reach the MPP and it is independently from the PV panel, although this

www.irjet.net p-ISSN: 2395-0072

e-ISSN: 2395 -0056

Volume: 03 Issue: 09 | Sep-2016

method may suffer from fast changes in environmental conditions.

Fig-3 Flowchart of the P&O Algorithm.

#### 2.CIRCUIT CONFIGURATION

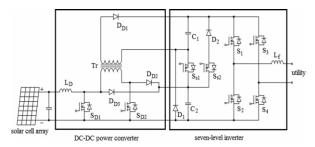

The proposed solar power generation system composed of a solar cell array, a dc-dc power converter, and a new seven-level inverter. The solar cell array is connected to the dc-dc power converter, and the dc-dc power converter is a boost converter that incorporates a transformer with a turn ratio of 2:1. The dc-dc power converter converts the output power of the solar cell array into two independent voltage sources with multiple relationships, which are supplied to the seven-level inverter. This new seven-level inverter is composed of a capacitor selection circuit and a full-bridge power converter, connected in a cascade.

Fig-4 Proposed solar power generation system

The power electronic switches of capacitor selection circuit determine the discharge of the two capacitors while the two capacitors are being discharged individually or in series. Because of the multiple relationships between then

voltages of the dc capacitors, the capacitor selection circuit outputs a three-level dc voltage. The full-bridge power converter further converts this three-level dc voltage to a seven-level ac voltage that is synchronized with the utility voltage. In this way, the proposed solar power generation system generates a sinusoidal output current that is in phase with the utility voltage and is fed into the utility, which produces a unity power factor. This new seven-level inverter contains only six power electronic switches, so the power circuit is simplified.

#### 2.1 DC-DC Power Converter

The DC-DC power converter incorporates a boost converter and a current-fed forward converter. The boost converter is composed of an inductor *LD*, a power electronic switch *SD*1, and a diode, *DD*3. The boost converter charges capacitor *C*2 of the seven-level inverter. The current-fed forward converter is composed of an inductor *LD*, power electronic

switches *SD*1 and *SD*2, a transformer, and diodes *DD*1 and *DD*2. The current-fed forward converter charges capacitor *C*1 of the seven-level inverter. The inductor *LD* and the power electronic switch *SD*1 of the current-fed forward converter are also used in the boost converter.

When SD1 is turned ON. The solar cell array supplies energy to the inductor LD. When SD1 is turned OFF and SD2 is turned ON. Accordingly, capacitor C1 is connected to capacitor C2 in parallel through the transformer, so the energy of inductor LD and the solar cell array charge capacitor C2 through DD3 and charge capacitor C1 through the transformer and DD1 during the off state of SD1. Since capacitors C1 and C2 are charged in parallel by using the transformer, the voltage ratio of capacitors C1 and C2 is the same as the turn ratio (2:1) of the transformer. Therefore, the voltages of C1 and C2 have multiple relationships. The boost converter is operated in the continuous conduction MO1

It should be noted that the current of the magnetizing inductance of the transformer increases when SD2 is in the ON state. Conventionally, the forward converter needs a third demagnetizing winding in order to release the energy stored in the magnetizing inductance back to the power source. However, in the proposed dc-dc power converter, the energy stored in the magnetizing inductance is delivered to capacitor C2 through DD2 and SD1 when SD2 is turned OFF. Since the energy stored in the magnetizing inductance is transferred forward to the output capacitor C2 and not back to the dc source, the power efficiency is improved. In addition, the power circuit is simplified because the charging circuits for capacitors C1 and C2 are integrated. Capacitors C1 and C2 are charged in parallel by using the transformer, so their voltages automatically have multiple relationships. The control circuit is also simplified. Thus complexity of the circuit is reduced.

# **International Research Journal of Engineering and Technology** (IRJET)

**Volume: 03 Issue: 09 | Sep-2016** www.irjet.net p-ISSN: 2395-0072

#### 2.2 Seven Level Inverter

As seen in Fig. 4, the seven-level inverter is composed of a capacitor selection circuit and a full-bridge power converter, which are connected in cascade. Operation of the seven-level inverter can be divided into the positive half cycle and the negative half cycle of the utility. For ease of analysis, the power electronic switches and diodes are assumed to be ideal, while the voltages of both capacitors C1 and C2 in the capacitor selection circuit are constant and equal to Vdc/3 and 2Vdc/3, respectively.

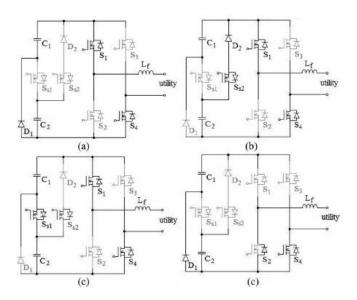

Since the output current of the solar power generation system will be controlled to be sinusoidal and in phase with the utility voltage, the output current of the seven-level inverter is also positive in the positive half cycle of the utility. The operation of the seven-level inverter in the positive half cycle of the utility can be further divided into four modes, as shown in Fig.5.

Fig-5. Operation in the positive half cycle

(a) mode 1 (b) mode 2 (c) mode 3 (d) mode 4

Mode 1: The operation of mode 1 is shown in Fig. 5(a). Both SS1 and SS2 of the capacitor selection circuit are OFF, so C1 is discharged through D1 and the output voltage of the capacitor selection circuit is Vdc/3. S1 and S4 of the fulbridge power converter are ON. At this point, the output voltage of the seven-level inverter is directly equal to the output voltage of the capacitor selection circuit, which means the output voltage of the seven-level inverter is Vdc/3.

Mode 2: The operation of mode 2 is shown in Fig. 5(b). In the capacitor selection circuit, SS1 is OFF and SS2 is ON, so C2 is discharged through SS2 and D2 and the output voltage of the capacitor selection circuit is 2Vdc/3. S1 and S4 of the full-bridge power converter are ON. At this point, the output voltage of the seven-level inverter is 2Vdc/3.

Mode 3: The operation of mode 3 is shown in Fig. 5(c). In the capacitor selection circuit, SS1 is ON. Since D2 has a reverse bias when SS1 is ON, the state of SS2 cannot affect the current flow. Therefore, SS2 may be ON or OFF, to avoiding switching of SS2. Both C1 and C2 are discharged in series and the output voltage of the capacitor selection circuit is Vdc. S1 and S4 of the full-bridge power converter are ON. At this point, the output voltage of the seven-level inverter is Vdc.

e-ISSN: 2395 -0056

Mode 4: The operation of mode 4 is shown in Fig. 5(d). Both SS1 and SS2 of the capacitor selection circuit are OFF. The output voltage of the capacitor selection circuit is Vdc/3. Only S4 of the full-bridge power converter is ON. Since the output current of the seven-level inverter is positive and passes through the filter inductor, it forces the antiparallel diode of S2 to be switched ON for continuous conduction of the filter inductor current. At this point, the output voltage of the seven level inverter is zero. Therefore, in the positive half cycle, the output voltage of the seven-level inverter has four levels:

Vdc, 2Vdc/3, Vdc/3, and 0.

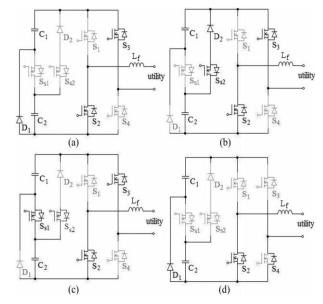

Fig-6. Operation in the negative half cycle

(a) mode 5 (b) mode 6 (c) mode 7 (d) mode 8

In the negative half cycle, the output current of the seven-level inverter is negative. The operation of the seven-level inverter can also be divided into four modes, as shown in Fig. 6. A comparison with Fig. 3 shows that the operation of the capacitor selection circuit in the negative half cycle is the same as that in the positive half cycle. The difference is that *S*2 and *S*3 of the full-bridge power converter are ON during modes 5, 6, and 7, and *S*2 is also ON during mode 8 of the negative half cycle. Accordingly, the output voltage of the capacitor selection circuit is inverted by the full-bridge power

© 2016, IRJET | Impact Factor value: 4.45 | ISO 9001:2008 Certified Journal | Page 424

Volume: 03 Issue: 09 | Sep-2016

www.irjet.net

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

converter, so the output voltage of seven level inverter also has four levels:

$V_{dc}$ ,  $2V_{dc}/3$ ,  $V_{dc}/3$ , 0,  $-V_{dc}/3$ ,  $-2V_{dc}/3$ , and  $-V_{dc}$ .

## 3. Experimental Results

To verify the performance of the proposed solar power generation system, a prototype was developed with a controller based on the DSP chip TMS320F28035. The power rating of the prototype is 500W, and the prototype was used for a single-phase utility.

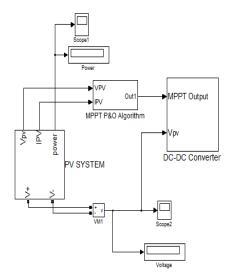

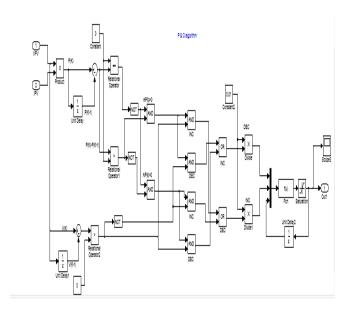

**Fig 7**: Simulink block diagram of solar power generation system

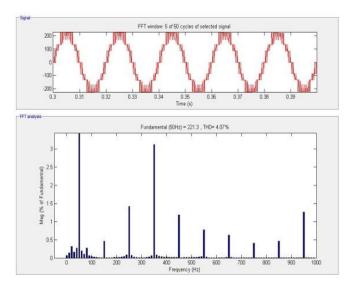

Simulation was done on MATLAB R2013a, the results was shown that the solar inverter has reduced harmonics.

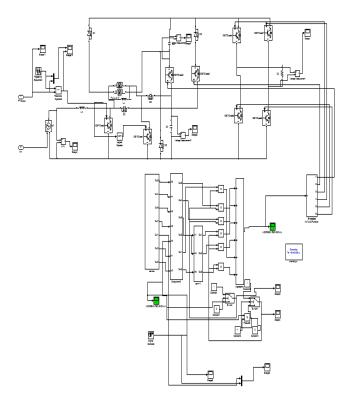

Fig.8 Simulink model of PV cell

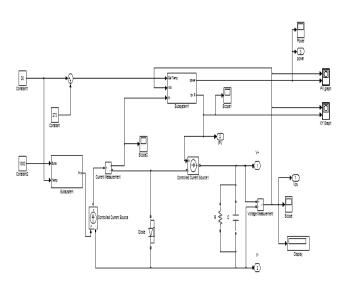

Fig.9 Simulink model of P & O algorithm

Fig.10 Simulink model of proposed seven level inverter

# **International Research Journal of Engineering and Technology** (IRJET)

Volume: 03 Issue: 09 | Sep-2016 www.irjet.net p-ISSN: 2395-0072

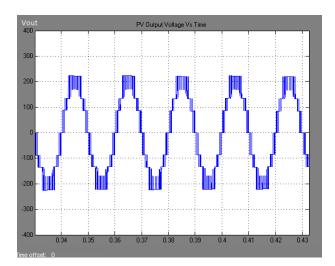

**Fig.11.** Output voltage of seven level inverter

Fig.12.THD Waveform

### 4. CONCLUSION

This paper proposes a solar power generation system to convert the DC energy generated by a solar cell array into AC energy that is fed into the utility. The proposed solar power generation system is composed of a DC/DC power converter and a seven-level inverter. The seven-level inverter contains only six power electronic switches, which simplifies the circuit configuration. Furthermore, only one power electronic switch is switched at high frequency at any time to generate the seven-level output voltage. This reduces the switching power loss and improves the power efficiency. The voltages of the two DC capacitors in the proposed sevenlevel inverter are balanced automatically, so the control circuit is simplified. Experimental results show that the proposed solar power generation system generates a sevenlevel output voltage and outputs a sinusoidal current that is in phase with the utility voltage, yielding a power factor of unity. In addition, the proposed solar power generation system can effectively trace the maximum power of solar cell array.

e-ISSN: 2395 -0056

#### REFERENCES

- [1] Buticchi, G.; Barater, D.; Lorenzani, E.; Concari, C.; Franceschini, G. A nine-level grid-connected converter topology for single-phase transformerless PV systems. *IEEE Trans. Ind. Electron.* 2014, *61*, 3951–3960.

- [2] Z. Zhao, M. Xu,Q. Chen, J. S. Jason Lai, and Y. H. Cho, "Derivation, analysis, and implementation of a boostbuck converter-based high-efficiency pv inverter," IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1304– 1313.

- [3] K. Hasegawa and H. Akagi, "Low-modulation-index operation of a five level diode-clamped pwm inverter with a dc-voltage-balancing circuit for a motor drive," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3495–3505,Aug. 2012

- [4] N. A. Rahim, K. Chaniago, and J. Selvaraj, "Single-phase seven-level grid-connected inverter for photovoltaic system," IEEE Trans. Ind. Electr. vol. 58, no. 6, pp. 2435–2443, Jun. 2011.

- [5] Jinn-Chang Wu, Member, IEEE, and Chia-Wei Chou, "Solar Power Generation system with a Seven-Level Inverter," IEEE Transactions on Power Electronics, vol. 29, no. 7, July 2014

- [6] Arango, E.; Ramos-Paja, C.A.; Calvente, J.; Giral, R.; Serna, S. Asymmetrical interleaved DC/DC switching converters for photovoltaic and fuel cell applications—Part1: Circuit generation, analysis and design. *Energies* 2012, *5*, 4590–4623.

- [7] Walker, G.R.; Sernia, P.C. Cascaded DC–DC converter connection of photovoltaic modules. In Proceedings of the 33rd Annual Power Electronics Specialists Conference, Cairns, Queensland, Australia, 22–27 June 2002; pp. 24–29.

- [8] E. Pouresmaeil, D. Montesinos-Miracle, O. Gomis-Bellmunt, "Control Scheme of Three-Level NPC Inverter for Integration of Renewable Energy Resources Into AC Grid," Syst. J., Vol.6, No.2, pp.242-253, 2012.

- [9] K. Hasegawa, H. Akagi, "Low-Modulation-Index Operation of a Five-Level Diode-Clamped PWM Inverter With a DC-Voltage-Balancing Circuit for a Motor Drive," *IEEE Trans. Power Electron.*, Vol. 27, No. 8, pp.3495-3505, 2012

- [10] J, M. Shen, H. L. Jou, J. C. Wu, "Novel Transformerless Grid-connected Power Converter with Negative Grounding for Photovoltaic Generation System," *IEEE Trans. Power Electronics*, Vol. 27, No. 4, pp.1818-1829, 2012

© 2016, IRJET | Impact Factor value: 4.45 | ISO 9001:2008 Certified Journal | Page 426

# **International Research Journal of Engineering and Technology** (IRJET)

Volume: 03 Issue: 09 | Sep-2016 www.irjet.net p-ISSN: 2395-0072

e-ISSN: 2395 -0056

### **BIOGRAPHIES**

NISHA XAVIER -PG Shcolar and completed B Tech in Electrical and Electronics Engineering in 2013 from SNM IMT Maliankara and presently pursuing M Tech in "Power Electronics" in KMEA Engineering College Edathala, Kerala, INDIA

SABEENA SALAM – Assistant Professor in KMEA Engineering COLLEGE EDATHALA,KERALA.She completed her B Tech in Electrical and Electronics Engineering and ME in "Power Electronics"

REMNA RADHAKRISHNAN – PHD Research Scholar in CUSAT.She completed her B Tech in Electrical and Electronics Engineering and M Tech in Industrial Drives and Control from Rajagiri School of Engineering and Technology, Ernakulam, Kerala,INDIA