e-ISSN: 2395-0056 Volume: 10 Issue: 07 | July 2023 www.irjet.net p-ISSN: 2395-0072

# **Experimental Electrical Characterization Results of PLL Jitter**

## Nidhi<sup>1</sup>, M. Ejaz Aslam Lodhi<sup>2</sup>, Mohd. Safdar Imam<sup>3</sup>

<sup>1</sup>M. Tech. Scholar, Department of ECE, Indira Gandhi Delhi Technical University for Women, Delhi, India <sup>2</sup>Senior Assistant Professor, Department of ECE, Indira Gandhi Delhi Technical University for Women, Delhi, India <sup>3</sup>Sr. Manager. ST Microelectronics Pvt Ltd. Greater Noida. India

**Abstract** - *In this letter, we aim to validate and check the* electrical characteristic of Analog IPs embedded in SoCs. Analog blocks are more prone to the external behavior because the human world can talk and think in an analog manner. Hence, not easy to satisfy the requirement from an analog point of view compared to digital circuits which can be simulated and tested. Furthermore, when an analog comes into the picture, the noise insertion and its interface connections start creating problems in satisfying the actual specifications. Electrical characteristics validated on SoCs are single period and long-term Jitter for PLLs and their functionality according to the specifications. Further, our work will be based on improving the test bench with automated test environment, since automation helps to reduce human errors and make the testing process more reliable.

Key Words: PLL, Jitter, Noise, Analog, SoC, Validation.

#### 1. INTRODUCTION

A phase-locked loop (PLL) is an electronic circuit that continuously modifies its voltage or voltage-driven oscillator's frequency to match that of an input signal. PLLs can produce, maintain, modulate, demodulate, filter, or recover a signal from a communications channel[1] that is "noisy" because data is being interrupted. PLLs (Phase-Locked Loops) are essential components in many wireless and radio frequency (RF) applications due to their ability to generate stable and precise frequencies. They play a crucial role in various communication systems and devices, including Wi-Fi routers, broadcast radios, walkie-talkie radios, televisions, and mobile phones. Here's a brief explanation of how PLLs are used in these applications, which further helps in low power and delay electronics device[8]. A PLL is used for clock generation inside SoC, and its working and application are pretty similar to a frequency synthesizer in a cellphone to match the cellphone frequency with desired frequency of reception of the message signal, then communication can take place. The core function of a PLL is to synchronize the phase and frequency of an output signal with that of a reference signal. This closed-loop feedback system allows the PLL to lock onto and track the phase and frequency of the reference signal, making it an essential tool in many applications. It is a system of analog and digital components connected in a "negative feedback" topology rather than a single component.

#### 2. PLL AND ITS BASIC BUILDING BLOCK

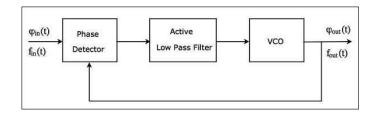

A PLL consists of three key components:

- 1. **Phase detector** (a phase comparator or mixer). It compares the phases of two signals and generates a voltage according to the phase difference. It multiplies the reference input and the voltagecontrolled oscillator output.

- 2. Voltage-controlled oscillator produces sinusoidal signal whose frequency matches closely the low-pass filter's centre frequency.

- 3. **Low-pass filter**: the loop filter plays a crucial role in smoothing and shaping the control voltage that is applied to the Voltage-Controlled Oscillator (VCO). Its primary function is to attenuate the highfrequency alternating current (AC) components of the phase detector's output signal while allowing the low-frequency components (DC) to pass through relatively unattenuated. This action smoothens and flattens the signal, making it more DC-like or continuous.

To better understand the operation, let's start with the basic building blocks of PLL

Figure 1: Basic Block Diagram of PLL

The phase detector (PD) compares the phase difference between the input signal's frequency (f\_ref) and the feedback signal's frequency (f\_out). It does not generate a DC voltage directly proportional to the phase difference, but rather it produces a voltage that represents the instantaneous phase error between these two signals.

The phase detector can be represented by a phase comparator or a multiplier. When using a multiplier as the

© 2023, IRJET **Impact Factor value: 8.226** ISO 9001:2008 Certified Journal Page 913

Volume: 10 Issue: 07 | July 2023 www.irjet.net p-ISSN: 2395-0072

phase detector, the output signal will contain two frequency components:

The sum frequency: This component is equal to f\_in + f\_out. It arises because the phase detector multiplies the input and feedback signals, producing the sum of their frequencies as one of the output components.

The difference frequency: This component is equal to |f\_in-f\_out|, where the absolute value is taken to ensure it is a positive frequency. This component also appears in the output because of the multiplication process in the phase detector..

When no input is supplied to a VCO, it generates a signal at a specific frequency. A DC voltage can be applied to this frequency to move it in either direction. The frequency deviation is thus directly related to this. The voltage-controlled oscillator signal is compared to the input/reference signal by the PLL. The PLL can identify frequency and phase discrepancies in the signals because it is frequency and phase sensitive. It produces or generates an error signal that reflects the phase difference in the transmission. The low-pass filter(LPF) uses this difference, which is an error signal to remove high-frequency components and convert the error signal to changing direct current (DC) levels. The voltage-controlled oscillator is subsequently given this "feedback signal" in order to regulate its frequency.

#### 3. JITTER AND ITS TYPES

Many of the signals inside a PLL, as well as those at the input and output, are binary signals. The jitter of binary signals is a frequent way to describe noise. An unwanted change or ambiguity in the timing of occurrences is known as jitter. Typically, the transitions in a signal are the events of interest.

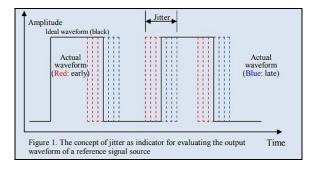

Figure 2: Jitter

Digital signal waveforms show up as a bright line on an oscilloscope. It is possible for this brilliant line, which should oscillate frequently, to appear thick at times. A jitter is indicated by the signal line expanding.

Figure 2 [2]depicts a single period, or cycle, of a signal containing numerous distinct periods. An ideal waveform exhibits a consistent and repetitive cycle. However, real-world waveforms vary in the time domain, with signal edges either rising or falling earlier (red) or later (blue) than expected. Jitter is introduced due to slight instabilities in electrical signal reading equipment and interference along signal-carrying paths. Excessive jitter can lead to interference between neighboring signals, resulting in a degradation of image and sound quality during transmission.

e-ISSN: 2395-0056

- 1. Types of Jitter: There are many types of jitter, including the following:

- Period jitter (peak to peak)

- RMS jitter

- Random jitter

- Deterministic jitter

- Accumulated jitter (long-term jitter)

We will be calculating period and long-term jitter. Period jitter (peak-to-peak jitter)

- 1.1. **Period jitter** is observed as variation width. Epson expresses this variation using a peak-to-peak value.

- 1.2. **RMS jitter** (1-sigma) The standard deviation (a) of the above measurement findings is used to calculate RMS jitter. This indicates a 68.26% chance that it exists within 12.5 p. Peak-to-peak jitter, on the other hand, only reveals a small percentage of states (many ms) in a crystal product that is typically used for an extended period of time and does not exhibit overall jitter. RMS jitter is only a meaningful measurement for an ideal normal distribution (Gaussian distribution); it is exceedingly unreliable for other distributions.

- 1.3. **Random jitter** (RJ) As the name suggests, random jitter is a jitter component that cannot be predicted. Random jitter can occur spontaneously as it is influenced by a device's characteristics, thermal noise, etc. Random jitter is expressed using standard deviation, using the expressions "right RJ" and "left RJ."

- 1.4. **Deterministic jitter (DJ),** Circuit design, electromagnetic induction, or the external environment can all induce bounded jitter. Actual measurement findings show that deterministic jitter is the part between right and left random jitter. To summarise the preceding jitter ideas, spontaneously induced jitter (RJ) and artificially induced jitter (DJ) are components of the overall jitter in a single cycle length. Reducing deterministic jitter is the key to decreasing jitter. When this component is optimized, the gap between the right and left RJ overlaps, allowing a perfect normal distribution to occur.

1.5. Accumulated jitter (long-term iitter) Accumulated jitter is a type of jitter that cannot be described as variations within a single cycle or period. Instead, it results from the cumulative effect of jitter fluctuations observed over numerous successive cycles. In this context, the horizontal axis of a jitter plot represents the number of measured cycles, while the vertical axis depicts the jitter's 1-sigma value for each cycle. Analyzing accumulated jitter allows us to observe the behavior of jitter over consecutive cycles. With accumulated cycles, there is a tendency for the 1sigma jitter values to converge or stabilize starting from a certain cycle. This means that as more cycles are considered, the jitter fluctuations tend to reach a relatively consistent level, providing insights into the long-term stability and behavior of the jitter phenomenon. This enables the PLL circuit bandwidth and transient response characteristics to be determined[2].

Jitter has an impact on the setup and hold of the route elements because it alters the circuit's clock delay and the amount of time the clock is available at sync points. Depending on whether the jitter makes the clock run faster or slower in a system that otherwise has clean timing, setup hold or setup violations may happen. As a result, the chip's functionality or performance will degrade and, when analysing timing, the designer must take into account the jitter values of the clock signal.

#### 4. VALIDATION METHODOLOGY OF PLL

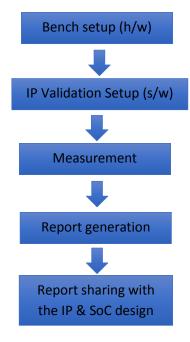

Figure 3: Validation Flow

PLL testing is an essential part of validation. Our primary focus is to use PLL inside the SoC to provide a variable frequency clock input to many blocks and the peripherals attached to SoC for their data transfer synchronization. In such architecture, PLL0 and PLL1 are connected in cascaded mode, and the source clock to PLL can be provided by any of the three available sources, i.e., IRC (16MHz), XOSC (40MHz), and externally by AWG.

e-ISSN: 2395-0056

The test execution is done in automation to avoid human errors. At the same time, it is also cumbersome for a human to collect so much data manually. All the bench instruments are connected together to the PC through the GPIB interface, an IEEE interface standard that allows control of the equipment remotely. The test automation is achieved through VBA (visual basic for application). A VBA script is written to control these instruments to change their voltage supply and temperature, capture the data through an oscilloscope and log them into the Excel report file and using pivot chart, we plot the graph to have the understanding of results .

### 4.1 Equipment Used to Perform Testing

- 1. 4GHz Oscilloscope

- 2. Precision Temperature Forcing System (PTFS)

- 3. Arbitrary Waveform Generator (80MHz) for applying external clock.

- 4. Lauterbach Debugger Hardware with JTAG connection interface.

- 5. Active probe. One end is connected to Oscilloscope, and another is connected to the PLL clock out probing point on Daughterboard.

#### 4.2 Validation Condition for IPs

Temperature:

Table -1: Temperature required for testing the PLL

|             | T ambient | T Hot    | T Cold   |  |  |

|-------------|-----------|----------|----------|--|--|

| DUT         | 25        | Max spec | Min spec |  |  |

| Temperature |           | plus 5C  | minus 5C |  |  |

Power Supply:

**Table -2:** Maximum and Minimum Power supply Required for testing the PLL

| V max   | V type | V min   |

|---------|--------|---------|

| VDD+10% | VDD    | VDD-10% |

© 2023, IRJET | Impact Factor value: 8.226 | ISO 9001:2008 Certified Journal | Page 915

Volume: 10 Issue: 07 | July 2023 www.irjet.net p-ISSN: 2395-0072

### Number of Samples:

The number of trials should be done on three samples to avoid discrepancies. It could be extended to more if the result is not compliant with the expected to ascertain if a particular observed issue is really present on the IP or not.

### 4.3 Types of Test Codes for PLL

There are two types of test codes under which the PLL is tested, Quiet Mode Code and Application like Code(Run\_Idd Mode).

In Quiet mode Code, all IPs present inside the SoC are not active, only the PLL under test is activated and a couple of other IPs are really needed for the SoC. Most of the IPs are kept under power down. At this time, fewer transistors are going through transitions, which means only a few are switching on - off. This assures that there is minimum noise generated inside the SoC, and PLL is minimally affected by the noise inside the SoC.

On the other hand, an Application like code (Run\_Idd Mode) is used, and most of the IPs inside the SoC are enabled/activated. This way, the maximum number of possible transistors are going through transitions means getting switched on – off. This creates noise inside the SoC and is normally the actual use case under which PLL has to work.

We perform the Jitter test on both types of codes. The parameters we measured in validations are Short-Term (Single Period) Jitter and Long-Term Jitter on both the PLLs, which are embedded inside the 32-bit microcontroller architecture SoC.

#### **4.4 Software Development**

A unique software code has to be developed by configuring the PLLs under test to generate the desired output clock frequency as per the test cases.

## 5. EXPERIMENTAL RESULTS

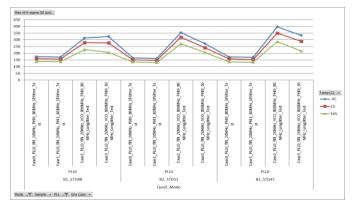

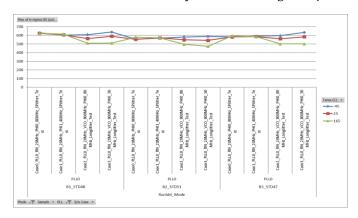

**Chart-1:** Single Period & Long Term Jitter PLL0: Quiet Mode

The above experimental results of consolidated Single Period Jitter and long term Jitter of PLLO Quiet Mode which made us to conclude that the results are under the specification provided by the design team which are:

e-ISSN: 2395-0056

| Case   | Type of<br>Jitter      | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max.<br>value<br>specified<br>by the<br>designer |

|--------|------------------------|-----------------------------------|-----------------------------------|--------------------------------------------------|

| Case 0 | Single<br>period       | 93.708<br>ps                      | 175.25<br>ps                      | 200 ps                                           |

| Case 1 | Single<br>period       | 89.448<br>ps                      | 171.468                           | 300 ps                                           |

| Case 2 | Long<br>term<br>Jitter | 149.594<br>ps                     | 397 ps                            | 500 ps                                           |

| Case 3 | Long<br>Term<br>Jitter | 127.746<br>ps                     | 330 ps                            | 500 ps                                           |

**Table-1:** Results of Single Period & Long Term Jitter PLL0 (Quiet Mode)

We can also conclude that the results of long term jitter are high as compared to single period jitter because of the obvious increased number of cycles used in long term jitter.

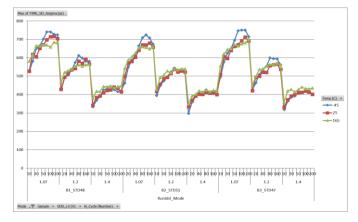

**Chart-2:** Single & Long Term Period Jitter PLL0: Run\_Idd\_Mode

The above experimental results of consolidated Single Period Jitter and long term Jitter of PLLO Run Idd Mode which made us to conclude that the results are not under the specification provided by the design team which are:

Volume: 10 Issue: 07 | July 2023 www.irjet.net p-ISSN: 2395-0072

| Case   | Type of<br>Jitter      | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max.<br>value<br>specified<br>by the<br>designer |

|--------|------------------------|-----------------------------------|-----------------------------------|--------------------------------------------------|

| Case 0 | Single<br>period       | 311.166<br>ps                     | 628.950<br>ps                     | 200 ps                                           |

| Case 1 | Single<br>period       | 304 ps                            | 613.632<br>ps                     | 300 ps                                           |

| Case 2 | Long<br>term<br>Jitter | 320.976<br>ps                     | 607.854<br>ps                     | 500 ps                                           |

| Case 3 | Long<br>Term<br>Jitter | 257.796<br>ps                     | 638.130<br>ps                     | 600 ps                                           |

**Table-2:** Results of Single & Long Term Period Jitter PLL0 (Run\_Idd\_Mode)

The reason behind the results are not under the specification are in Run Idd mode is employed

- The majority of the SoC's IPs are turned on or activated. In this manner, the most transistors possible are switching on and off or passing through transitions.

- This causes noise inside the SoC and is typically the use case that PLL has to operate in.

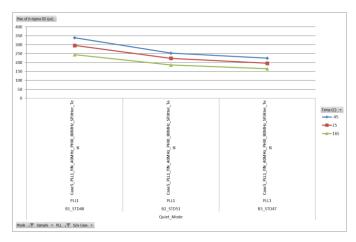

Chart-3: Single Period Jitter PLL1: Quiet Mode

The above experimental results of Single Period Jitter of PLL1 Quiet Mode which made us to conclude that the results are under the specification provided by the design team, which is:

| Case   | Type of<br>Jitter | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max. value<br>specified<br>by the<br>designer |

|--------|-------------------|-----------------------------------|-----------------------------------|-----------------------------------------------|

| Case 5 | Single<br>period  | 105.522<br>ps                     | 338.934<br>ps                     | 500 ps                                        |

e-ISSN: 2395-0056

Table-3: Results of Single Period Jitter PLL1(Quiet Mode)

Chart-4: Single Period Jitter PLL1:Run\_Idd\_Mode

The above experimental results of Single Period Jitter of PLL1 Run Idd Mode which made us to conclude that the results are under the specification provided by the design team, which is:

| Case   | Type of<br>Jitter | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max. value specified by the designer |

|--------|-------------------|-----------------------------------|-----------------------------------|--------------------------------------|

| Case 5 | Single<br>period  | 187.602<br>ps                     | 378.474<br>ps                     | 500 ps                               |

**Table-4:**Results of Single Period Jitter PLL1(Run\_Idd\_Mode)

- All three samples(SoC) used during the testing of are following almost similar trend, which makes us to justify that the results we are getting are accurate and can be used.

- one thing we can observe in the graph that we are getting lower standard deviation at the temperature 165 C at the hottest.

Volume: 10 Issue: 07 | July 2023 www.irjet.net p-ISSN: 2395-0072

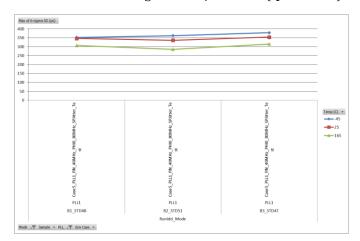

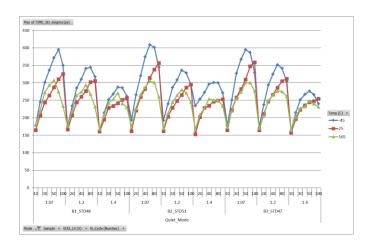

Chart-5: Long Term Jitter PLL0: Quiet Mode

The above experimental results of Single Period Jitter of PLL0 Quiet Mode which made us to conclude that the results are under the specification provided by the design team, which is:

| Case   | Type of<br>Jitter      | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max. value specified by the designer |

|--------|------------------------|-----------------------------------|-----------------------------------|--------------------------------------|

| Case 4 | Long<br>term<br>Jitter | 153.012<br>ps                     | 408 ps                            | 1000 ps                              |

Table-5: Results of Long Term Jitter PLL0 (Quiet Mode)

- All three samples(SoC) used during the testing of are following almost having similar behaviour, which makes us to justify that the results we are getting are accurate and can be used.

- One thing we can observe in the graph that we are getting lower standard deviation at the temperature -45 C at the min temperature.

Chart-6: Long Term Jitter PLL0 (Run\_Idd Mode)

The above experimental results of Long term Jitter of PLL0 Run Idd Mode which made us to conclude that the results are under the specification provided by the design team, which

e-ISSN: 2395-0056

| Case   | Type of<br>Jitter   | Min.<br>Value<br>after<br>testing | Max.<br>Value<br>after<br>testing | Max. value<br>specified by<br>the<br>designer |

|--------|---------------------|-----------------------------------|-----------------------------------|-----------------------------------------------|

| Case 4 | Long term<br>Jitter | 297.534<br>ps                     | 750.456<br>ps                     | 1000 ps                                       |

Table-6: Results of Long Term Jitter PLL0 (Run\_Idd Mode)

All three samples(SoC) used during the testing of are following almost similar trend, which makes us to justify that the results we are getting are accurate.

|     | PLL Parameter                                                                                                               |     | Design<br>stankent o |         | Measured | Result  | Ueit | PLL Jitter |                                                        | Conditions                                                                                                                                                                                                                                    | Receits and Notes                                                                                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|----------------------|---------|----------|---------|------|------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|     | Cett.0                                                                                                                      | Mis | Тур                  | Msz     | Mis      | Msz     | _    | Test       | VAT                                                    | PLL Conditions                                                                                                                                                                                                                                |                                                                                                       |

|     | PLLO PHIO Single Period State (6-Signa) with Guist Mode Code<br>Cacob: PLLO_FM_20MHz_PHIO_00MHz_SPJitter_Text               |     |                      | 200.00  | 93,198   | 115.254 | ps   | PLL0-P190  |                                                        | Fig. 2000 (Extend),<br>Fills PRESY (1902.2), FFEPH. A,<br>RECOMM. O. FILL FIND. 1000 FLIE. NO                                                                                                                                                 |                                                                                                       |

|     | PLLO PHIO Single Period State (6-Signa) with Ros_bid Code<br>Cacol: PLLO_HR_20MHs_PHIO_00MHs_SP.State_Text                  |     |                      | 200.00  | 511.166  | 628.950 | ps   | PLLO-P190  |                                                        | TOPPIN, System cloth PLL0 (1879b); Clack<br>Ontac Ped (PC) - 6879b                                                                                                                                                                            |                                                                                                       |

|     | PLLO PHII Single Period Steer (6-Signa) with Quiet Made Code<br>Casel: PLLO_FIN_2OMNS_PHII_60MHS_SPStees_Test               |     |                      | 330.00  | 83.448   | 171.460 | ps   | PLLO-PHL1  |                                                        | Fig. 2000 County,<br>Fills PRESW (1900-20, FF2PHI A,<br>SEDDMIN AS FILE PRO-SHIPE, FILE PHI S                                                                                                                                                 |                                                                                                       |

|     | PLLO PHII Single Period Sitter (6-Sigma) with Rossidd Code<br>Casel: PLLO_FIN_20MRs_PHII_60MHs_SPSitter_Test                |     |                      | 200.00  | 204.716  | 613.632 | ps   | PLLO-PHL1  |                                                        | 4094s, PLL9, VCO - IROPERs, Eymun clark<br>-PLL9(IROPEs), Clark Ovi an Full (PEZ) -<br>4094s                                                                                                                                                  |                                                                                                       |

|     | PLLO PHIO Long Term Jitter (4-Signs) with Onice Mode Code<br>Cased:<br>PLLO_FIN_20MID_VCO_SOOMID_PHIO_DOMID_LongJitter_Text |     |                      | 500.00  | 143.544  | 337.080 | ps   | PLLO-P190  | Ydd_LY (Ceroffil<br>Yofrogi) = 1877, 124,<br>1487      | Fig. 200900 Council,<br>File PRINT APPLIES, PEPSES,<br>FEDERAL PRINT, PRINT, PRINT, POS-<br>FRIPTE, STANDON, PLACE (PRINT), CO-<br>COUNTY, STANDON, PLACE (PRINT), CO-<br>COUNTY, STANDON, PLACE (PRINT), CO-<br>COUNTY, PARTY (PT 1), 19996. | Single Period Jitter is measur<br>80MHz slock output on PAD<br>make it equivalent Long Term<br>Jitter |

| LLO | PLLO PHIO Long Term Jitter (4-Signs) with Ross Lidd Code<br>Cased:<br>PLLO_FIIL_COMID_VCO_BOOMID_PRIO_BOMID_LongJitter_Test |     |                      | 500.00  | 220.976  | 607.054 | ps   | PLLO-PHIO  | Vd4_HV = 5V<br>Temp = 450, 250, 950<br>Semples = 3-570 |                                                                                                                                                                                                                                               | Single Pretod Jitter is means<br>80MHz slock output on PAG<br>make it equivalent Long Ten<br>Jitter   |

|     | PLLO PHIO Long Term Jitter (4-Signs) with Oniet Mode Code<br>Costs:<br>PLLO_FIN_20MID_VCO_800MID_PHIO_50MID_LongJitter_Test |     |                      | 600.00  | 127.746  | 999,912 | ps   | PLLO-PHIO  |                                                        | Fig. 2000(Count).                                                                                                                                                                                                                             | Single Period Jitter is meass:<br>50MHz slock output on PAC<br>make it equivalent Long Yes<br>Jitter  |

|     | PLIG PHIO Long Term Jitter (4-Sigms) with Res_16d Code<br>Code3:<br>PLIG_PHI_20MHIS_VCO_800MHIS_PHIO_50MHIS_LongJitter_Test |     |                      | 600.00  | 257.196  | 638.130 | ps   | PLLO-PHIO  |                                                        | RECOMMO NO, PLLE, PROD-SOMMO, PLLE, NOD-<br>SOMMO, System dead, PLLO(MINNO); Clade<br>Owner Pat (PEZ) - SWING                                                                                                                                 | Single Period Jitter is measur<br>50MHz slock output on PAE<br>make it equivalent Long Term<br>Jitter |

|     | PLIO PHIO Long Term Jitter (4-Sigms) with Gaiet Mode Code<br>Cacel:<br>PLIO_HM_20MHs_VCO_SOOMHs_PHIO_40MHs_LongAtter_Test   |     |                      | 1000.00 | 153.012  | 400.034 | ps   | PLLO-P190  |                                                        | Fin-2009ks (Entervall)<br>File-2009ks (Entervall)<br>File-2009ks (1992-40) FFEMALIN<br>MCCO-4009ks (1912-40) File-200<br>(PEZ)-4004ks (Fyrlandels) FILE-4004ks                                                                                | Long Term Jitter is measured<br>40MHz slock output on PAE<br>200 clock cycles                         |

|     | PLLO PHIO Long Term Jimer (6-Sigms) with Res_166 Code<br>Cared:<br>PLLO_FIN_2OMMs_VCO_SOOMMs_PHIO_40MHs_LongJitter_Test     |     |                      | 1000.00 | 297.534  | 750.456 | ps   | PLLO-PHIO  |                                                        |                                                                                                                                                                                                                                               | Long Term Jitter is measured<br>40MHz slock output on PAD<br>200 clock cycles                         |

|     | PLLI PHI Single Period Jitter (6-Signa) with Oniet Mode Code<br>CaseS: PLLI_SIN_40MILe_PRIO_00MILe_SPJitter_Test            |     |                      | 500.00  | 105.522  | 338,834 | po   | PLL1-PHI   | Voltage) = 107V, 12V,<br>140V<br>Vd4_HV = 5V           | Fig. 6899kg(Suburud)<br>PLLL 1950-20, FFDPHS S, PLLL 1946-1949kg.<br>PLLL 1500, DMMMs, Maddatan, Studda S.                                                                                                                                    |                                                                                                       |

|     | PLLI PHI Single Period Jitter (6-Signs) with Res_Idd Code<br>Cords: PLLL_FIR_40MHz_PRIO_50MHz_SPJAtter_Test                 |     |                      | 500.00  | 187,602  | 318,414 | pt   | PUL1-PHI   | Forten desk-P                                          | System desk (FLL1(1999ks), Systlesk Ovien.<br>Fel(PE)-1999s                                                                                                                                                                                   |                                                                                                       |

Chart-7: Results of PLL

#### 6. CONCLUSIONS

Once the measurements are done, data is plotted, and the result is analyzed. After analyzing the plotted results, it's observed that all samples tested follow almost the same temperature and voltage variations trends. By checking their minimum & maximum values, we can conclude that the results are within the design specifications or not under the tested VT conditions.

It's observed that jitter with application like code (Run\_Idd), is much higher with respect to the quiet mode code, because a lot more transistors are switching, creating more noise inside the SoC in the former case.

PLL Jitter also increases if unwanted noise is generated by any particular IP inside the SoC, affecting the PLL

Thermal noise, power supply changes, loading situations, device noise, and interference coupled with surrounding circuits also contribute to jitter.

www.irjet.net p-ISSN: 2395-0072

e-ISSN: 2395-0056

Table -3: Results of the PLL

**Volume: 10 Issue: 07 | July 2023**

| Test<br>Overview                                                                      | Condition                                                                                                                                       | Results                                                                |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| The test<br>aimed to<br>check the<br>single<br>period<br>and long-<br>term<br>jitter. | Temp: - 40C, 25C, 165C VDD-HV; 3V, 6V VDD-LV:1.07V, 1.2V, 1.40V Fin: 20/40MHz, Fref=Xosc VCO: 800MHz PLL0 PHI: 40/80MHz Clock out on Pad: 40MHz | Within specification Min Variation: - 0.00215% Max Variation: +0.0125% |

#### **REFERENCES**

- [1] Awati, Rahul, and John Burke. "What Is a Phase-Locked Loop(PLL)?" *Networking*, 14 June 2021, www.techtarget.com/searchnetworking/definition/pha se-locked-loop.

- [2] Jenkins, Julian. "Specifying a PLL Part 2: Jitter Basics."

Design And Reuse, www.designreuse.com/articles/48875/specifying-a-pll-jitterbasics.html. Accessed 15 July 2023.

- [3] Maneatis, John G. "Low-jitter process-independent DLL and PLL based on self-biased techniques." *IEEE journal of solid-state circuits* 31.11 (1996): 1723-1732.

- [4] Georgoulopoulos, Nikolaos and Alkiviadis A. Hatzopoulos. "UVM-based Verification of a Digital PLL Using SystemVerilog." 2019 29th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS) (2019): 23-28.

- [5] D. C. Lee, "Analysis of jitter in phase-locked loops," in IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 49, no. 11, pp. 704-711, Nov. 2002, doi: 10.1109/TCSII.2002.807265.

- [6] (Jitter and Phase Noise, n.d.)

- [7] Telba, A.A. & Qasim, Syed Manzoor. (2011). Experimental Investigation of Low-Jitter and Wide-Band Dual Cascaded PLL System. 10.1063/1.3627194.

- [8] Harshita Gehlot, Mohd Ejaz Aslam Lodhi, "Analysis of Proposed FinFET Based Full Adder using CMOS Logic Style", International Research Journal of Engineering and Technology, Vol. 6, (04), April 2019.