Volume: 10 Issue: 03 | Mar 2023 www.irjet.net

p-ISSN: 2395-0072

# **Improved Nine-Level Transformerless Inverter with Reduced Part** Count

# Mohar singh meena, Neeraj kumawat, Dheeraj Verma

Student YIT jaipur Assistant professor Department of Electrical engineering Research Scholar (Ph.D. Student, Department of Electrical Engineering, Malviya National Institute of Technology, *Jaipur, Rajasthan, India.*)

**Abstract** - An PV inverter systems improve in terms of efficiency using transformerless inverter topologies but new problem related to Galvanic isolation need to be dealt with it. The electrical unit provides galvanic isolation and eliminates leakage current, thus preventing direct current from entering the network. The main disadvantage of using a transformer is that it significantly reduces the It o ered a transformer-free connection that is cost- effective, space-saving, and more energy efficient. When galvanic insulation is restored in a transformerless connection, the leakage current increases and therefore the PWM methods and topologies used

transformerless inverter, multilevel, Kev Words: leakage current....

#### 1. INTRODUCTION

Among all green resources, solar electrical energy (PV) is one of the cleanest, quickest, and most widely available energy sources. The cost of the PV system is continuously falling thanks to technological advances in manufacturing processes and materials, making it the most economical energy source for large-scale planning in the future. Through their increased use of green energy, a number of nations (including the USA, Germany, China, Japan, Australia, France, Italy, Spain, etc.) have already started to reap the benefits. In the Asian country, the market for renewable energy may expand quickly. As of the end of February 2020, the nation had a total installed capacity of 34.404 GW

for solar energy. A twenty GW capability goal set by the Indian government for 2022 was met four years earlier than anticipated. To connect the PV panels to the grid, the grid-connected PV systems require power inverters, which are typically Galvanic isolated and non-isolated inverters are two different classifications. Galvanic isolation is typically achieved in the isolated type using a highfrequency DC side transformer or a low-frequency AC side electrical device, which increases system safety overall. Transformerless inverters have attracted a lot of interest from the domestic market because of their low to medium power capacity cost [1], size/weight, and increased efficiency

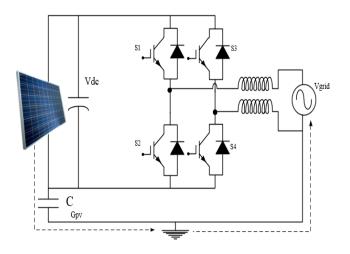

1.1 H Bridge topology with bipolar PWM two half-bridges, the H-bridge is a fundamental topology. Motor drives and UPS have both utilized this topology. Several PWM techniques can be applied to control the four switches in this arrangement. The simplest is a bipolar PWM, which modulates the extra switches in relation to one another and generates an output voltage with two levels (+ V and -V). The line current makes its way back to the DC link capacitor during the freewheeling phase, which lowers the conversion efficiency.

If we select the FFT for this design, we can see that there are significant voltage spikes that result in parasitic capacitances. Consequently, a significant amount of leakage current. Since the solar generator's parasitic capacitance controls the leakage current in this instance, the leakage current cannot be influenced by the output filter. The H-bridge with bipolar modulation, having a line filter with inductances evenly distributed between the line and the neutral, and having a bipolar PWM strategy ensures constant common mode voltage, while PV ground voltage only varies as a function of grid[9] frequency with an amplitude equal to half the peak value of the mains voltage. This makes it suitable for photovoltaic systems without a transformer. Conversion efficiency is the only limitation, as was previously mentioned.

Half bridge topology

Volume: 10 Issue: 03 | Mar 2023 www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Figure 1 FFT of half bridge topology

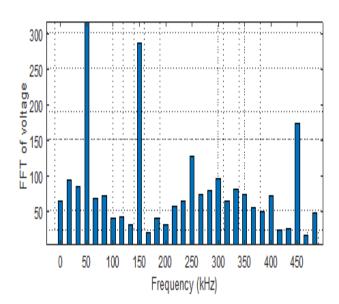

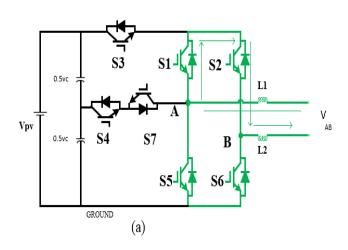

### **HERIC TOPOLOGY**

The computer system combines all of the benefits of unipolar PWM with common-mode behaviour in bipolar PWM, and it also offers high efficiency.

The idea of a highly efficient and dependable inverter (HERIC) has changed the topology of the H-bridge, as previously mentioned[18].A diode connects each series of 2 extra switches (S5-S6) that are part of the alteration. As illustrated in figure the photoelectric generator is detached from the network over the full zero voltage vector when S5, S6, or ar glows while S1, S2, S3, and 4 hundredths are all in their off states. Because the switching frequency will not be the high-frequency change occurring on the DC terminals, an interruption occurs in the construction of the zero-voltage vector, resulting in a unipolar output voltage with an equivalent frequency. photoelectric power plant. Additionally, the inverter efficiency stays high because, depending on the direction of the mains current, the load current short circuits through S5 or S6 during the freewheeling period.

Figure 2 HERIC topology

Volume: 10 Issue: 03 | Mar 2023 www.irjet.net p-ISSN: 2395-0072

Figure 3 Simulation of heric topology

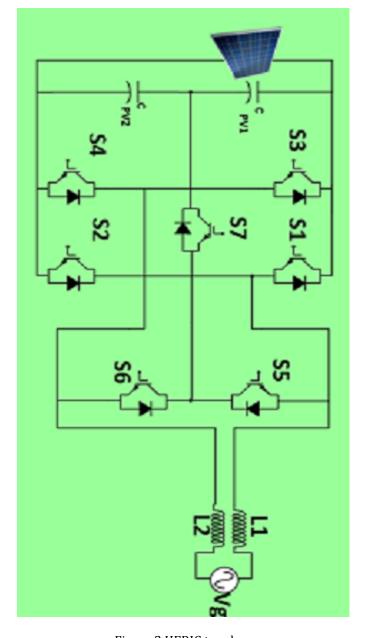

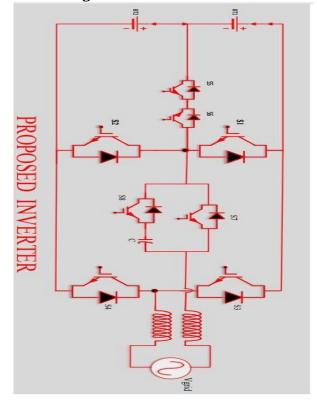

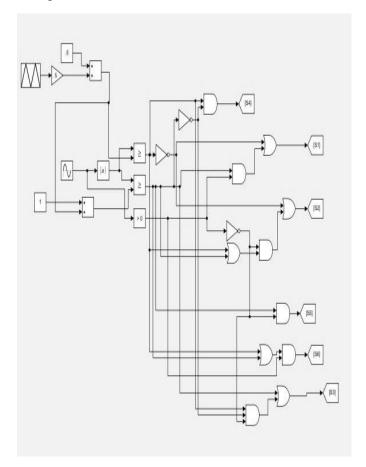

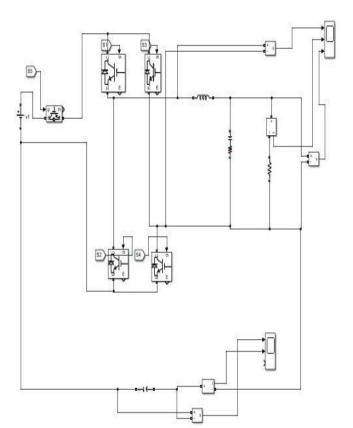

### 1.2PROPOSED TOPOLOGY

Fig 1 displays the circuit schematic for the suggested inverter topology. There are seven MOSFET switches in total: S1, S2, S3, S4, S5, S6, and S7. HSPWM, or hybrid sinusoidal PWM, is the modulation method employed. Vpv is a representation of a photovoltaic panel. For filtering, an L-L filter is employed. The electrical grid is represented by V grid. The input dc link capacitance is represented by Cin and is divided into two equally sized components by c pv 2. PV grid-tied systems can link the suggested inverter design, which can lower [2] leakage currents by maintaining consistent common mode voltages. Because they use transformers, traditional half-bridge inverter topologies do not require a fixed common mode voltage. Transformer omission results in a galvanic connection between the grid and the solar panels.

#### 1.2 Switching Table

| State | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$ | $v_{out}$                    |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|------------------------------|

| $L_1$ | 1     | 0     | 1     | 0     | 1     | 0     | 0     | 1     | $2V_{dc}$                    |

| $L_2$ | 0     | 0     | 0     | 1     | 0     | 1     | 1     | 1     | $3V_{\underline{dc}\over 2}$ |

| $L_3$ | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | $V_{dc}$                     |

| $L_4$ | 0     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | $V_{\frac{dc}{2}}$           |

| $L_5$ | 1     | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 0                            |

| $L_6$ | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 0     | $-V_{\underline{dc}\over 2}$ |

| $L_7$ | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 1     | $-3V_{\underline{dc}}$       |

| $L_8$ | 0     | 1     | 0     | 0     | 1     | 0     | 0     | 0     | $-2V_{dc}$                   |

| $L_9$ | 1     | 1     | 1     | 0     | 1     | 0     | 1     | 1     | $-V_{dc}$                    |

e-ISSN: 2395-0056

Sample paragraph, The entire document should be in cambria font. Type 3 fonts must not be used. Other font types may be used if needed for special purposes. The entire document should be in cambria font. Type 3 fonts must not be used. Other font types may be used if needed for special purposes.

#### 2. Circuit diagram

operational description

Volume: 10 Issue: 03 | Mar 2023

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Common mode voltage causes leakage current to terminate directly. Leakage current will be kept to a minimum [3] if we keep the common mode voltage constant. In general current in a capacitor is defined by  $i_{\rm Leakage} = c \ d({\rm constant})/{\rm dt} = 0$

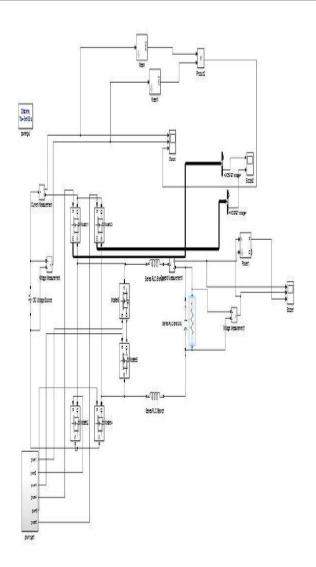

## **Simulation**

Figure (a) H6 topology

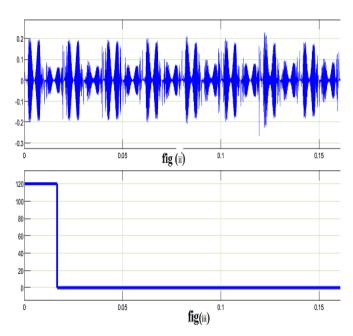

Figure iv,iii leakage current rms value and average value

Figure iv simulation model of H5 topology

Figure v Common mode voltage and output voltage of h5 topology

0.23

0.235

0.24

0.245

0.25

0.255

Figure vi PWM signals for gate pulse of h5 topology

0.21

0.205

0.215

0.22

0.225

e-ISSN: 2395-0056

# **International Research Journal of Engineering and Technology** (IRJET)

Volume: 10 Issue: 03 | Mar 2023 www.irjet.net p-ISSN: 2395-0072

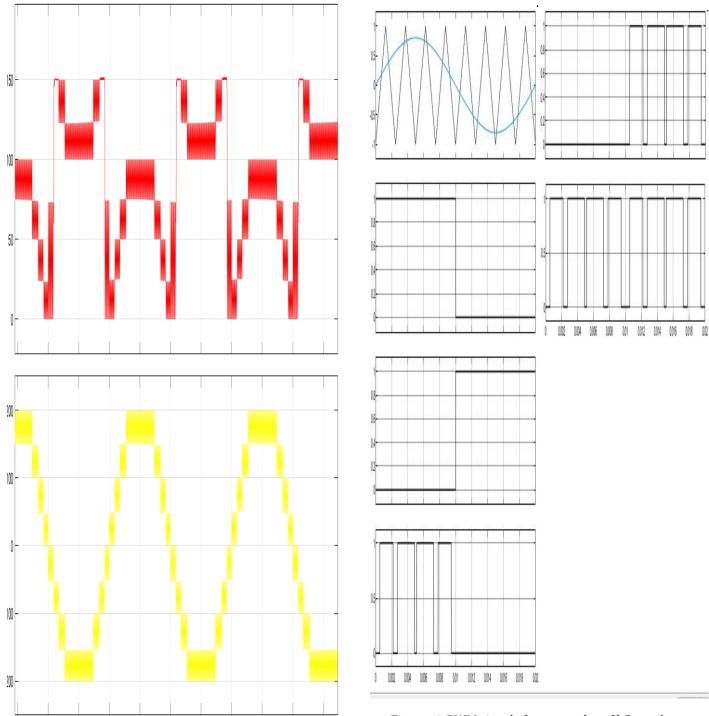

Figure v Nine level output from proposed inverter, load current

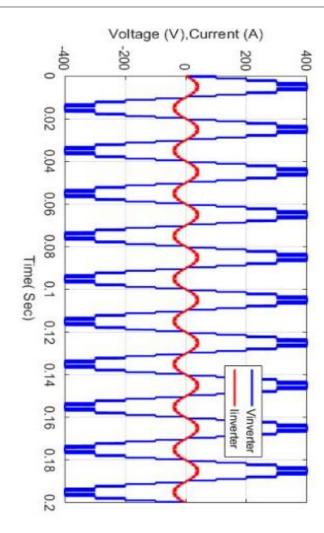

I have taken resistive load in simulation. I've utilised 400 v dc. I've got two outputs here. which is figure iii displays the terminal output of my inverter without a filter and fig displays the output of the inverter with an inductor acting as the filter.

I used 300 nf capacitors and 3 mh inductors, and the output of the inverter with the filter is only sinusoidal. Without the filter, the output is Nine stepped waveforms. Levels with steps are. Matlab Simulink model is the simulation platform of choice.

#### 3. CONCLUSIONS

An inverter may be used to feed the alternative energy to the grid. The topologies of inverters with and without galvanic isolation are completely different from conventional inverter. different transformerless inverter topologies are used for analysis, design, and simulation purposes during this work, first I have used H-5 topology, and then H-6 topology, at last I have simulate proposed topology Results that meet the objectives are measured after simulating the circuit. Simulated experiments are also used to test the leakage current. I got leakage current in permissible limits.in my model I got leakage current 4 micro ampere.

e-ISSN: 2395-0056

## **REFERENCES**

- [1] Islam, Monirul, Saad Mekhilef, and Mahamudul Hasan. "Single phase transformerless inverter topologies for grid-tied photovoltaic system: A review." *Renewable and sustainable energy reviews* 45 (2015): 69-86.

- [2] Islam, Monirul, Saad Mekhilef, and Mahamudul Hasan. "Single phase transformerless inverter topologies for grid-tied photovoltaic system: A review." *Renewable and sustainable energy reviews* 45 (2015): 69-86.

- [3] Araújo, Samuel Vasconcelos, Peter Zacharias, and Regine Mallwitz. "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems." *IEEE Transactions on Industrial Electronics* 57.9 (2009): 3118-3128.

- [4] Zeb, Kamran, et al. "A review on recent advances and future trends of transformerless inverter structures for single-phase grid-connected photovoltaic systems." *Energies* 11.8 (2018): 1968.

- [5] Yang, Bo, et al. "Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system." *IEEE transactions on power electronics* 27.2 (2011): 752-762.

- [6] Gu, Bin, et al. "High reliability and efficiency single-phase transformerless inverter for grid-connected photovoltaic systems." *IEEE Transactions on Power Electronics* 28.5 (2012): 2235-2245.

- [7] Zeb, Kamran, et al. "A review on recent advances and future trends of transformerless inverter structures for single-phase grid-connected photovoltaic systems." *Energies* 11.8 (2018): 1968.

- [8] Yang, Bo, et al. "Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system." *IEEE transactions on power electronics* 27.2 (2011): 752-762.

- [9] Siwakoti, Yam P., and Frede Blaabjerg. "Commonground-type transformerless inverters for single-phase solar photovoltaic systems." *IEEE Transactions on Industrial Electronics* 65.3 (2017): 2100-2111.

# **International Research Journal of Engineering and Technology** (IRJET)

IRJET Volume: 10 Issue: 03 | Mar 2023 www.irjet.net p-ISSN: 2395-0072

[10] Ardashir, Jaber Fallah, et al. "A single-phase transformerless inverter with charge pump circuit concept for grid-tied PV applications." *IEEE* Transactions on Industrial Electronics 64.7 (2016): 5403-5415.

e-ISSN: 2395-0056